#### Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

11-12-2019 2:00 PM

# Split DC bus converters for power electronic and AC-DC Microgrid applications

Javad Khodabakhsh, The University of Western Ontario

Supervisor: Gerry Moschopoulos, *The University of Western Ontario* A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering © Javad Khodabakhsh 2019

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Power and Energy Commons

#### **Recommended Citation**

Khodabakhsh, Javad, "Split DC bus converters for power electronic and AC-DC Microgrid applications" (2019). *Electronic Thesis and Dissertation Repository*. 6692. https://ir.lib.uwo.ca/etd/6692

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

#### Abstract

Power electronic converters are used extensively for electrical power conversion in applications such as renewable energy systems, utility applications, and electric vehicles. Such converters are needed as it is rare for a source voltage to fit the needs of a load or a set of loads for any particular application. They consist of active semiconductor switches and passive components that are combined in circuit structures (topologies) that are operated with a control strategy. The focus of this thesis is on AC-DC and DC-DC converters and their applications in AC-DC microgrids.

AC-DC converters are typically two-stage converters that consist of a front-end AC-DC converter followed by a DC-DC back-end converter. The AC-DC front-end converter converts AC voltage from an AC source such as the grid to a DC bus voltage that has been filtered by an intermediate DC bus capacitor; the DC-DC converter then converts this DC voltage into the desired output voltage. A less expensive alternative to this two-stage approach is to have just one converter perform AC-DC and DC-DC conversion.

This thesis examines isolated single-stage AC-DC converters and back-end DC-DC converters for two-stage converters that have a split DC bus, with either two capacitors in series across the bus to split the voltage or with two parallel current paths to split the bus current. These converters have fewer components or fewer light-load losses than converters with conventional topologies. Four new power converters with a split DC bus are proposed in this thesis: a reduced-switch three-phase AC-DC converter, two lower power DC-DC converters, and an AC-DC converter that can be used to simplify the architecture and control of AC-DC hybrid microgrids. The proposed converters increase efficiency and reduce the control complexity of hybrid microgrids.

The operation of each converter is explained, the steady-state characteristics and the dynamic model of each converter are determined by mathematical analysis, and a procedure that can be used for their power and control stages design is developed. Experimental and simulation results are used to confirm the feasibility of the converters and simplified AC-DC hybrid microgrid, and conclusions that resulted from the thesis work are stated.

#### Lay Summary

Power electronic converters are the electronic circuits that are used to process the electric power in applications such as renewable energy systems, utility applications, and electric vehicles. Such converters are used to interface different electricity generators and consumers. Since electricity is generated in two forms of AC and DC, there are four types of power electronic converters: AC-DC, AC-AC, DC-AC, and DC-DC. This thesis focuses on AC-DC and DC-DC converters.

Some of these converters are built by combining two converters so-called "front-end" and "back-end" converters to perform more complex power processing. Such a structure increases the overall system cost. More advanced structure for the converters are proposed in the literature to offer the same performance with only one converter that reduces the overall system cost, such converters are called "single-stage" converters.

This thesis investigates single-stage AC-DC converters and back-end DC-DC converters for two-stage converters that are using a new structure (split DC bus). These converters are less expensive and more efficient than conventional converters. Four new power converters are proposed in this thesis with the new structure.

The operation of each converter is explained; the mathematical model of the converters is derived. Experimental and simulation results are used to confirm the feasibility of the proposed converters in this thesis.

**Keywords:** Hybrid AC-DC microgrids, power electronics, DC-DC converters, three-phase single-stage AC-DC converters, split DC bus converters

#### Acknowledgments

I would like to thank my supervisor, Dr. Gerry Moschopoulos, for his helpful supervision, and inspiration during my Ph.D. studies.

Besides, I would like to thank the Ph.D. exam committee: Dr. Raveendra K. Rao, Dr. Firouz Badrkhani Ajaei, Dr. Styliani Constas, and Dr. David Xu for their comments.

I would like to thank Ms. Michelle Wagler, the Administrative Officer in the Department of Electrical and Computer Engineering and Ms. Stephanie Tigert, the Graduate Coordinator for their great help during my Ph.D. program.

Moreover, I would like to thank my family and my parents for their support. This thesis is dedicated to my great parents and family.

| Abstracti                                                                                         |  |  |  |

|---------------------------------------------------------------------------------------------------|--|--|--|

| Acknowledgmentsiv                                                                                 |  |  |  |

| Table of Contents                                                                                 |  |  |  |

| List of Tablesix                                                                                  |  |  |  |

| List of Figures x                                                                                 |  |  |  |

| Acronymsxiii                                                                                      |  |  |  |

| Chapter 1                                                                                         |  |  |  |

| 1 Introduction                                                                                    |  |  |  |

| 1.1 DC-DC converters                                                                              |  |  |  |

| 1.1.1 ZVS-PWM full-bridge converter                                                               |  |  |  |

| 1.1.2 Three-leg full-bridge converter                                                             |  |  |  |

| 1.2 AC-DC converters 11                                                                           |  |  |  |

| 1.2.1 Two-stage isolated AC-DC converters                                                         |  |  |  |

| 1.2.2 Front-end AC-DC converters for two-stage AC-DC converters                                   |  |  |  |

| 1.2.3 Single stage isolated three-phase AC-DC converters                                          |  |  |  |

| 1.3 Hybrid AC-DC Microgrids                                                                       |  |  |  |

| 1.4 Thesis Objectives                                                                             |  |  |  |

| 1.5 Thesis Outline                                                                                |  |  |  |

| Chapter 2                                                                                         |  |  |  |

| 2 Using Multilevel ZVZCS Converters to Improve Light-Load Efficiency in Low Power<br>Applications |  |  |  |

| 2.1 Introduction                                                                                  |  |  |  |

| 2.2 Example TL-ZVZCS DC-DC converter operation                                                    |  |  |  |

| 2.3 Comparison of TL and ZVS-PWM-FB Converters                                                    |  |  |  |

| 2.3.1 ZVS range                                                                                   |  |  |  |

### Table of Contents

|   |       | 2.3.2   | Efficiency                                                      | 34 |

|---|-------|---------|-----------------------------------------------------------------|----|

|   | 2.4   | Experi  | imental Results                                                 | 37 |

|   | 2.5   | Conclu  | usion                                                           | 42 |

| C | napte | er 3    |                                                                 | 44 |

| 3 |       | -       | f T-Type and ZVS-PWM Full-Bridge Converters for Switch-Mode P   |    |

|   | 3.1   | Introd  | uction                                                          | 44 |

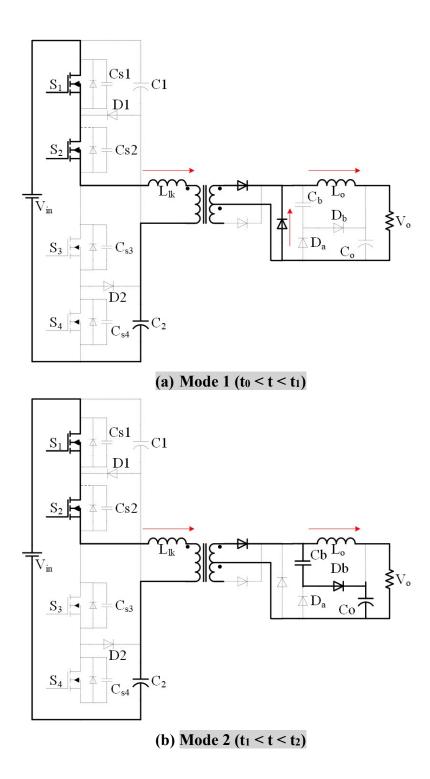

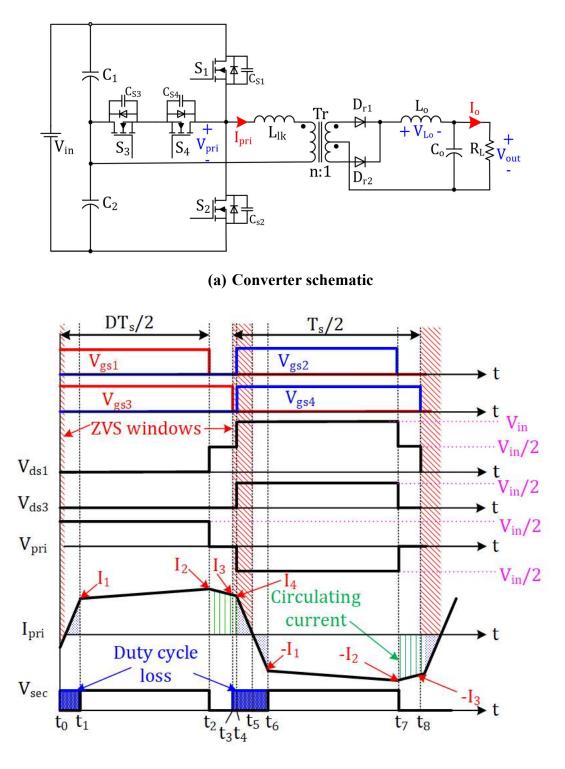

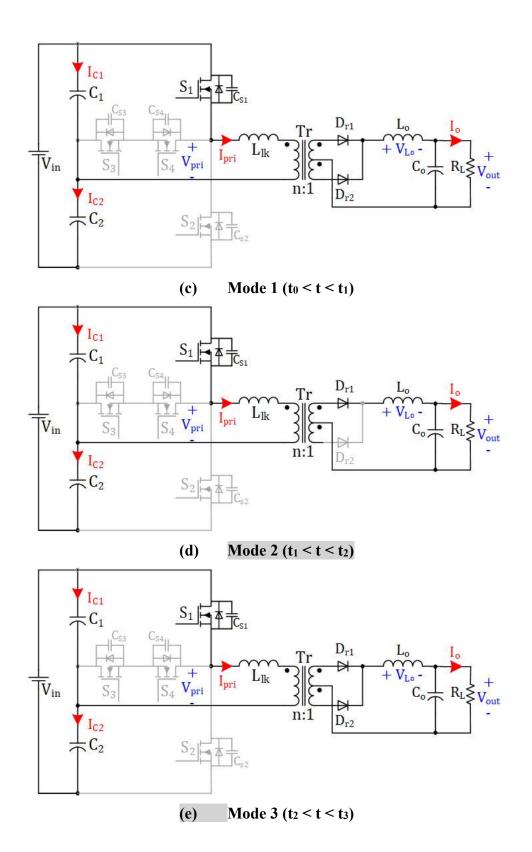

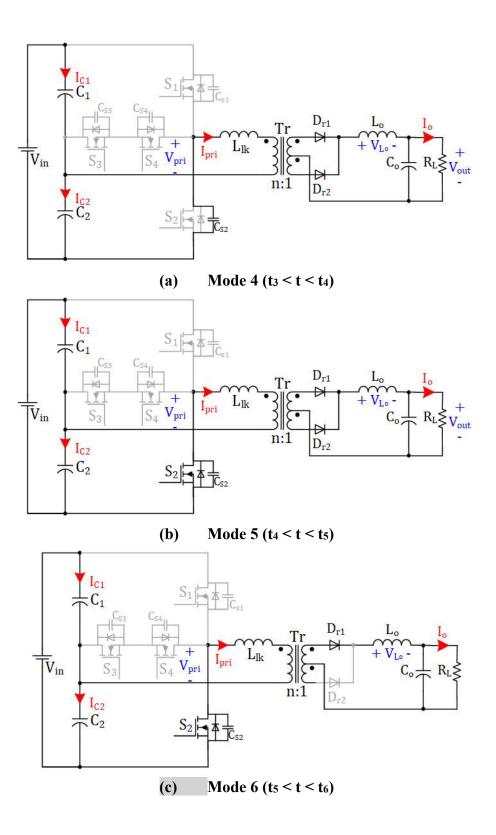

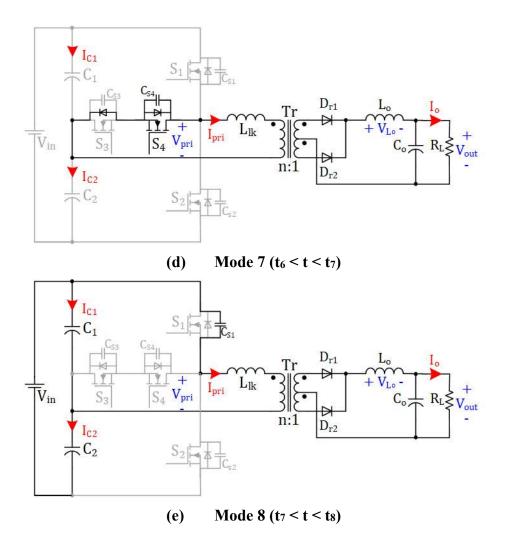

|   | 3.2   | Operat  | tion Principles                                                 | 44 |

|   | 3.3   | Conve   | erter Features                                                  | 54 |

|   | 3.4   | Т-Тур   | e converter design                                              | 55 |

|   |       | 3.4.1   | Voltage divider capacitors (C <sub>1</sub> and C <sub>2</sub> ) | 55 |

|   |       | 3.4.2   | High voltage switches (S <sub>1</sub> and S <sub>2</sub> )      | 56 |

|   |       | 3.4.3   | Low voltage switches (S <sub>3</sub> and S <sub>4</sub> )       | 56 |

|   |       | 3.4.4   | Transformer turns ratio (n) and leakage inductance $(L_{lk})$   | 57 |

|   | 3.5   | Comp    | arison of T-Type and ZVS-PWM-FB Converters                      | 57 |

|   |       | 3.5.1   | Magnetic component size                                         | 58 |

|   |       | 3.5.2   | ZVS operation region                                            | 60 |

|   |       | 3.5.3   | Duty cycle loss                                                 | 61 |

|   |       | 3.5.4   | Efficiency comparison                                           | 61 |

|   | 3.6   | Experi  | imental Results                                                 | 66 |

|   | 3.7   | Conclu  | usion                                                           | 70 |

| C | napte | er 4    |                                                                 | 72 |

| 4 | Fou   | r switc | h AC-DC converter with galvanic isolation                       | 72 |

|   | 4.1   | Introd  | uction                                                          | 72 |

|   | 4.2   | Conve   | erter operation                                                 | 72 |

|   |       | 4.2.1   | AC-DC converter                                                 | 75 |

|    |                                                                             | 4.2.2                                                                                               | DC-DC converter                                                                                                                                                                                                                                                                                                                                   | 77                                                       |

|----|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    | 4.3                                                                         | Conve                                                                                               | rter Features                                                                                                                                                                                                                                                                                                                                     | 80                                                       |

|    | 4.4                                                                         | Conve                                                                                               | rter control                                                                                                                                                                                                                                                                                                                                      | 83                                                       |

|    | 4.5                                                                         | Conve                                                                                               | rter Design                                                                                                                                                                                                                                                                                                                                       | 84                                                       |

|    |                                                                             | 4.5.1                                                                                               | DC blocking capacitor C <sub>b</sub>                                                                                                                                                                                                                                                                                                              | 85                                                       |

|    |                                                                             | 4.5.2                                                                                               | RMS current of the switches                                                                                                                                                                                                                                                                                                                       | 85                                                       |

|    |                                                                             | 4.5.3                                                                                               | Transformer turns ratio (n)                                                                                                                                                                                                                                                                                                                       | 86                                                       |

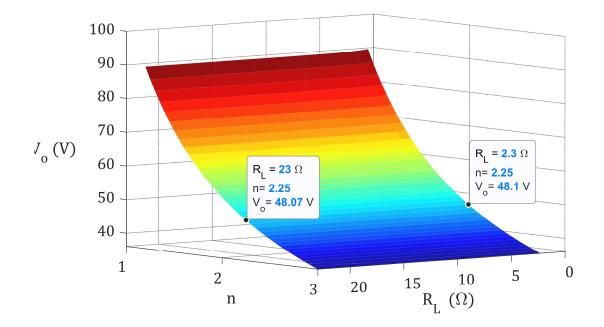

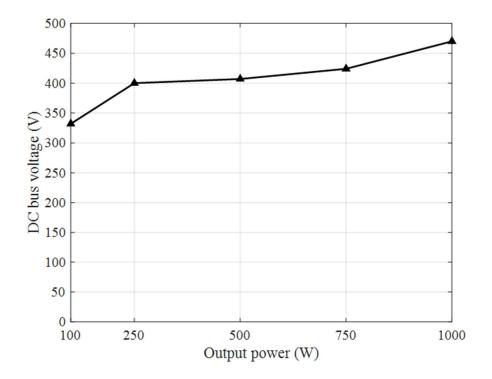

|    |                                                                             | 4.5.4                                                                                               | DC bus voltage                                                                                                                                                                                                                                                                                                                                    | 92                                                       |

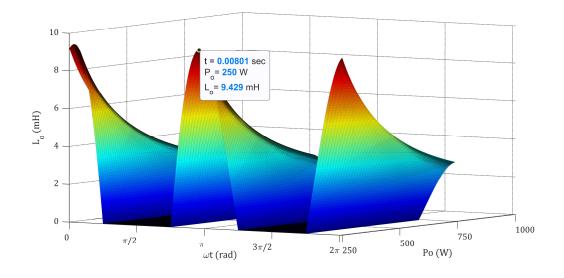

|    |                                                                             | 4.5.5                                                                                               | ZVS range                                                                                                                                                                                                                                                                                                                                         | 96                                                       |

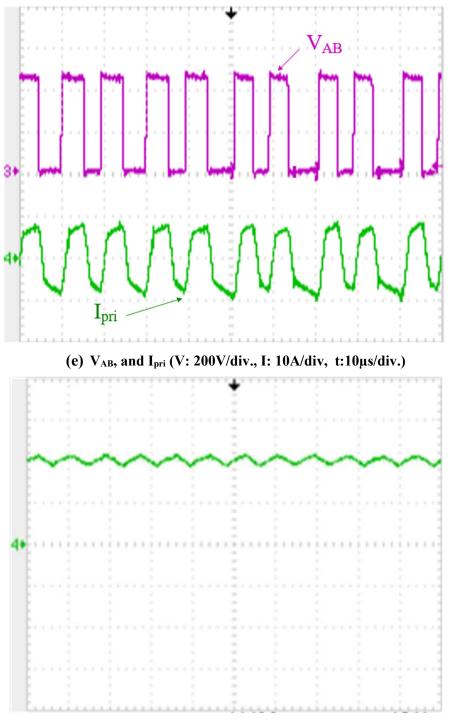

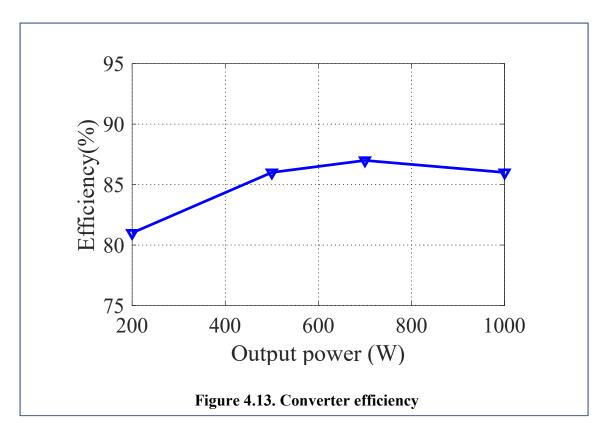

|    | 4.6                                                                         | Simula                                                                                              | tion and Experimental results                                                                                                                                                                                                                                                                                                                     | 97                                                       |

|    | 4.7                                                                         | Conclu                                                                                              | nsion                                                                                                                                                                                                                                                                                                                                             | 06                                                       |

| Cl | hapte                                                                       | er 5                                                                                                |                                                                                                                                                                                                                                                                                                                                                   | 08                                                       |

| 5  | Sim                                                                         | plified                                                                                             | Hybrid AC-DC Microgrid with a Novel Interlinking Converter                                                                                                                                                                                                                                                                                        | 08                                                       |

| -  |                                                                             | -                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   |                                                          |

| -  |                                                                             | -                                                                                                   | action                                                                                                                                                                                                                                                                                                                                            |                                                          |

| -  | 5.1                                                                         | Introdu                                                                                             | iction                                                                                                                                                                                                                                                                                                                                            | 08                                                       |

| -  | 5.1                                                                         | Introdu                                                                                             |                                                                                                                                                                                                                                                                                                                                                   | 08<br>10                                                 |

|    | 5.1                                                                         | Introdu<br>Simpli                                                                                   | fied HMG Structure and its components1                                                                                                                                                                                                                                                                                                            | 08<br>10<br>10                                           |

|    | 5.1<br>5.2                                                                  | Introdu<br>Simpli<br>5.2.1<br>5.2.2                                                                 | fied HMG Structure and its components                                                                                                                                                                                                                                                                                                             | 08<br>10<br>10<br>11                                     |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC                                                        | fied HMG Structure and its components                                                                                                                                                                                                                                                                                                             | 08<br>10<br>10<br>11<br>19                               |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC                                                        | fied HMG Structure and its components                                                                                                                                                                                                                                                                                                             | 08<br>10<br>10<br>11<br>19<br>20                         |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC<br>MP-IC                                               | fied HMG Structure and its components                                                                                                                                                                                                                                                                                                             | 08<br>10<br>10<br>11<br>19<br>20<br>20                   |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC<br>5.4.1<br>5.4.2                                      | fied HMG Structure and its components                                                                                                                                                                                                                                                                                                             | 08<br>10<br>10<br>11<br>19<br>20<br>20<br>22             |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC<br>5.4.1<br>5.4.2                                      | fied HMG Structure and its components       1         System-level simplification       1         Proposed MP-IC       1         features       1         control and design       1         BADSC control       1         UDDSC modelling and design       1                                                                                     | 08<br>10<br>10<br>11<br>19<br>20<br>20<br>22<br>26       |

|    | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul>                   | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC<br>MP-IC<br>5.4.1<br>5.4.2<br>Simula                   | fied HMG Structure and its components       1         System-level simplification       1         Proposed MP-IC       1         features       1         control and design       1         BADSC control       1         UDDSC modelling and design       1         ation and experimental results       1                                      | 08<br>10<br>11<br>19<br>20<br>20<br>22<br>26<br>26       |

|    | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Introdu<br>Simpli<br>5.2.1<br>5.2.2<br>MP-IC<br>MP-IC<br>5.4.1<br>5.4.2<br>Simula<br>5.5.1<br>5.5.2 | fied HMG Structure and its components       1         System-level simplification       1         Proposed MP-IC       1         features       1         control and design       1         BADSC control       1         UDDSC modelling and design       1         ation and experimental results       1         Experimental results       1 | 08<br>10<br>11<br>19<br>20<br>20<br>22<br>26<br>26<br>30 |

| 6 Summary and Conclusion |                           | 135 |  |

|--------------------------|---------------------------|-----|--|

|                          | 6.1 Summary               | 135 |  |

|                          | 6.2 Conclusion            | 137 |  |

|                          | 6.3 Contributions         | 138 |  |

|                          | 6.4 Suggested Future Work | 139 |  |

| Re                       | eferences                 | 140 |  |

| Cı                       | Curriculum Vitae          |     |  |

### List of Tables

| Table 3-1: Specification of the converter components | . 67 |

|------------------------------------------------------|------|

|                                                      |      |

| Table 5-1: Parameters of the simulated system        | 131  |

## List of Figures

| Figure 1.1. ZVS-PWM-FB DC-DC converter                                                               | 3  |

|------------------------------------------------------------------------------------------------------|----|

| Figure 1.2. ZVS-PWM-FB DC-DC converter typical waveforms                                             | 4  |

| Figure 1.3. Power losses in a typical switch during turn-on process. (a) without ZVS, (b) ZVS        |    |

| Figure 1.4. ZVZCS-PWM-FB DC-DC converter                                                             | 7  |

| Figure 1.5. Thee leg ZVS-PWM-FB DC-DC converter                                                      | 12 |

| Figure 1.6. circuit diagram of a typical two-stage isolated AC-DC converter structure                | 14 |

| Figure 1.7. Isolate AC-DC converter proposed in [30]                                                 | 14 |

| Figure 1.8. Isolate three-phase AC-DC converter with a boost DC-DC stage                             | 16 |

| Figure 1.9. Isolate three-phase AC-DC converter by using the reduced switch conv<br>proposed in [38] |    |

| Figure 1.10. Single stage AC-DC converters and their associated waveforms                            | 19 |

| Figure 1.11. Single stage AC-DC converters                                                           | 20 |

| Figure 1.12. DC system with Intermediate Bus Architecture (IBA) [62]                                 | 23 |

| Figure 2.1. FB-ZVS-PWM DC-DC converter                                                               | 27 |

| Figure 2.2. TLDC-DC converter with secondary clamp circuit                                           | 29 |

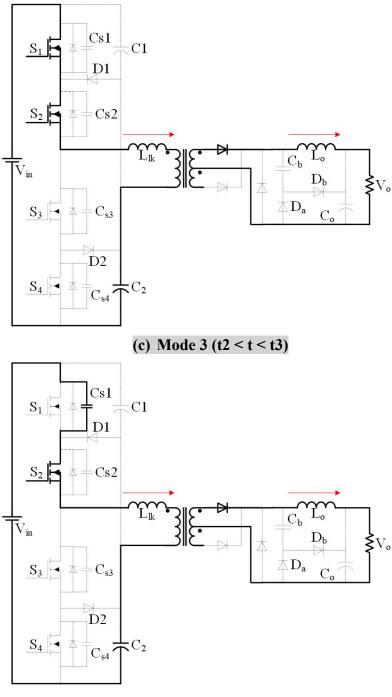

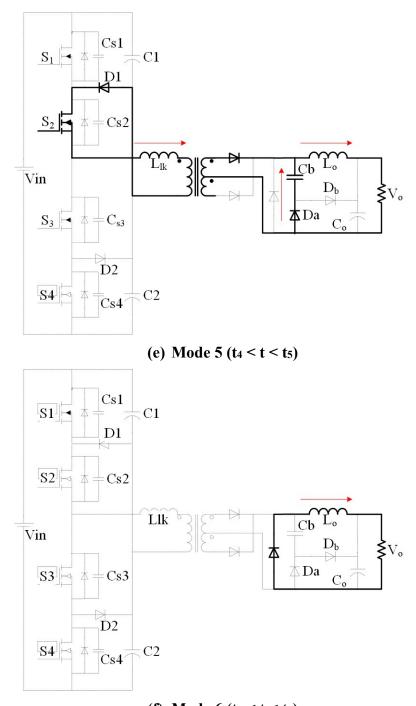

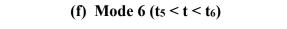

| Figure 2.3. TL DC-DC converter modes of operation                                                    | 33 |

| Figure 2.4. Start of freewheeling mode of operation                                                  | 35 |

| Figure 2.5. Typical waveforms of the TL DC-DC converter                                              | 37 |

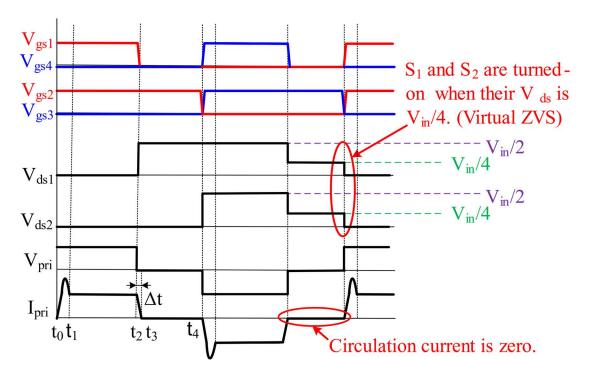

| Figure 2.6. TL-ZVZCS converter waveforms                                                             | 40 |

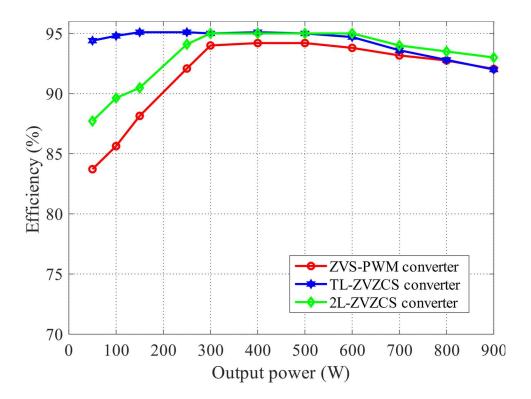

| Figure 2.7. Three-level and two-level converter efficiency comparison                                              | 41  |

|--------------------------------------------------------------------------------------------------------------------|-----|

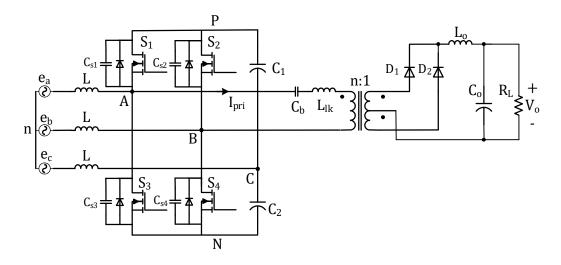

| Figure 3.1. The ZVS T-type DC-DC converter                                                                         | 46  |

| Figure 3.2. The ZVS T-type DC-DC converter modes of operation                                                      | 53  |

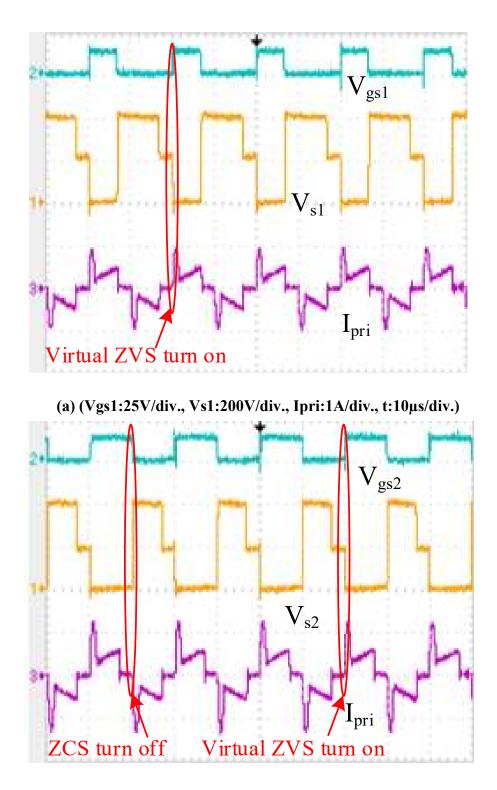

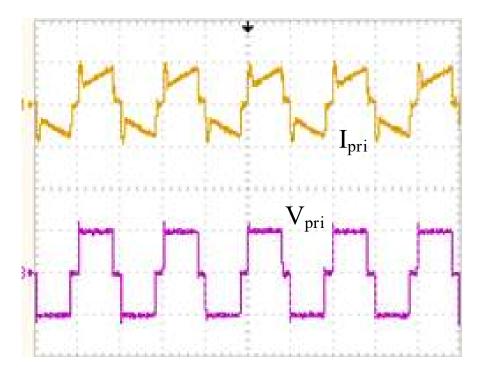

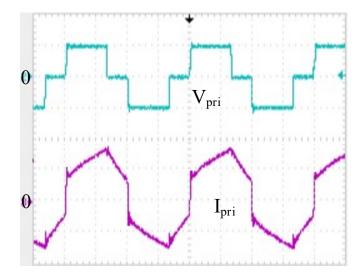

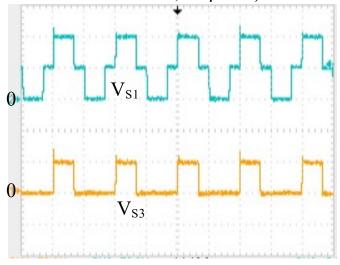

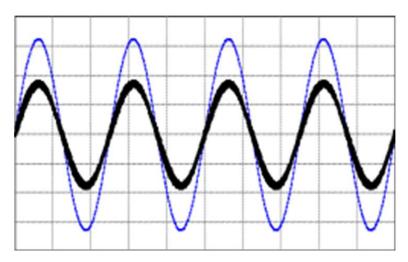

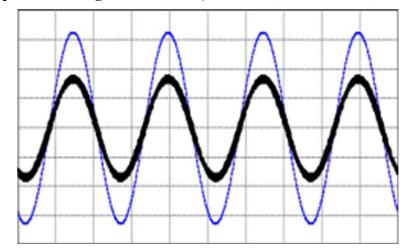

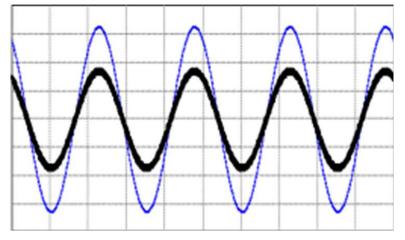

| Figure 3.3. Typical converter waveforms of a ZVS T-type converter                                                  | 68  |

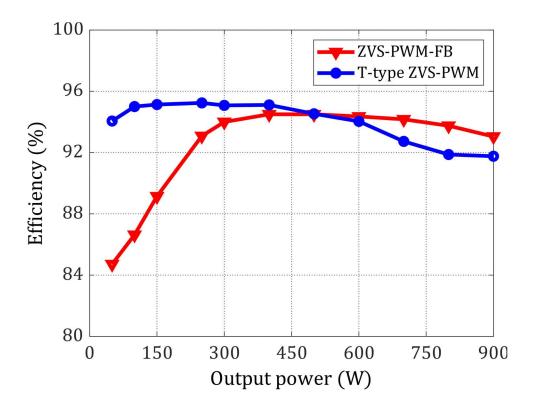

| Figure 3.4. Graph of efficiency vs output power for the full bridge-ZVS-PWM and converters                         | • 1 |

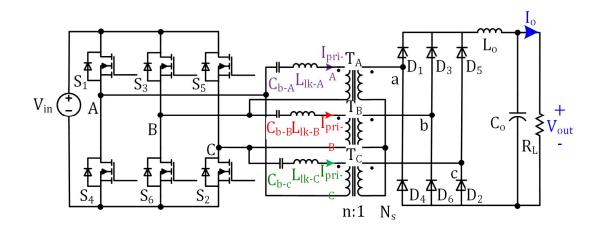

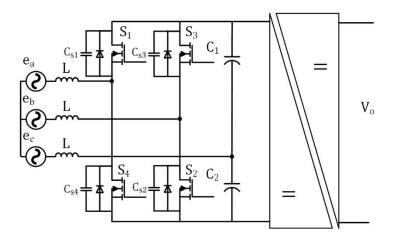

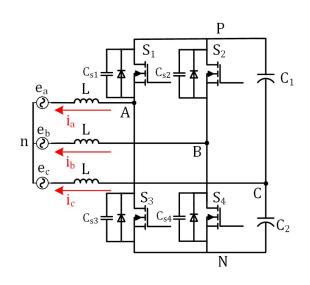

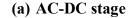

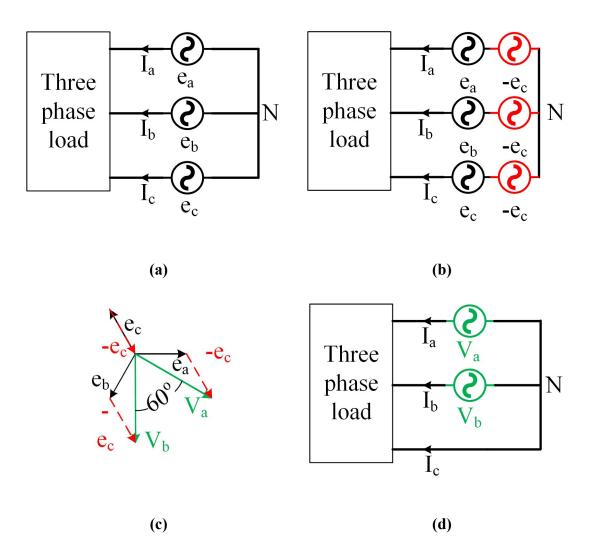

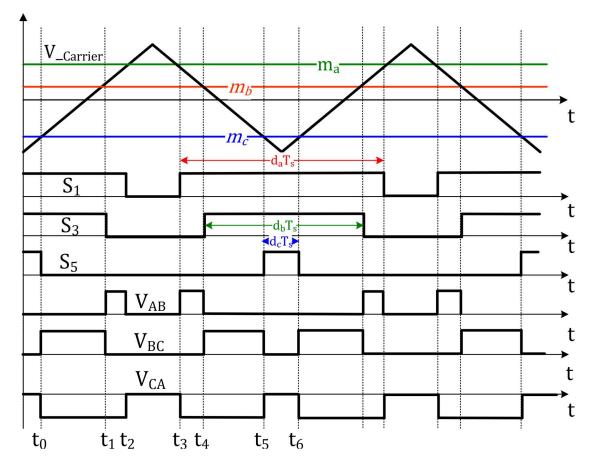

| Figure 4.1. Proposed three-phase AC-DC single-stage converter                                                      |     |

| Figure 4.2. AC-DC converter stages                                                                                 | 74  |

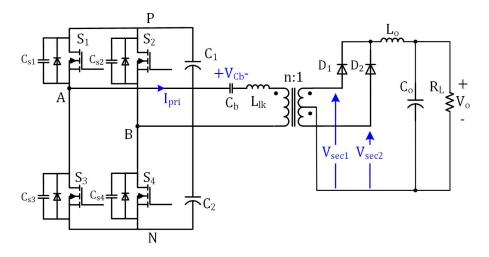

| Figure 4.3. Three phase load supply by two voltage sources                                                         | 76  |

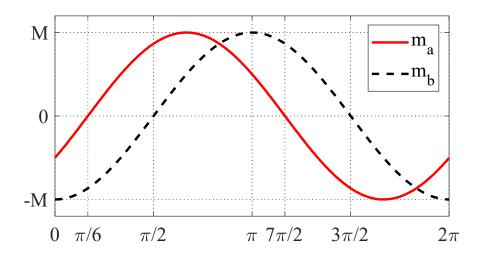

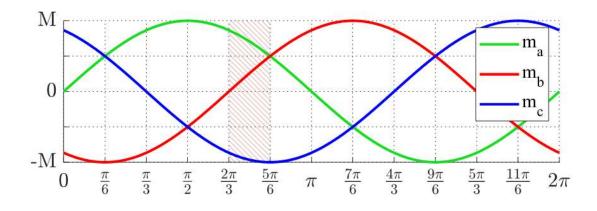

| Figure 4.4. Modulation signals in line frequency                                                                   | 77  |

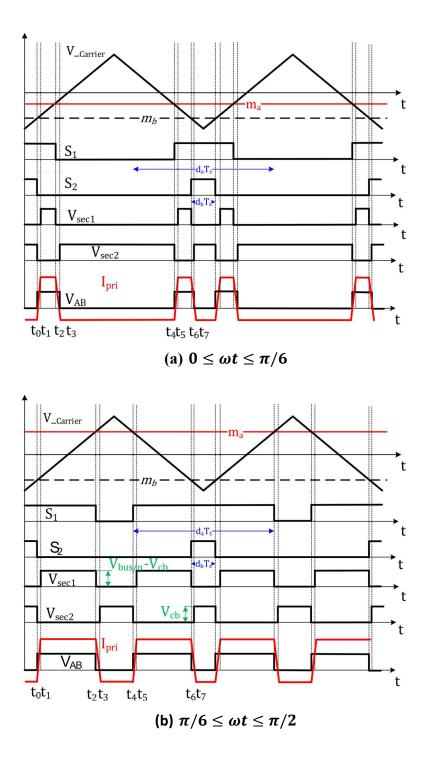

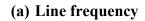

| Figure 4.5. Modulation signals in switching frequency scale, gate signals, secondary v primary voltage and current |     |

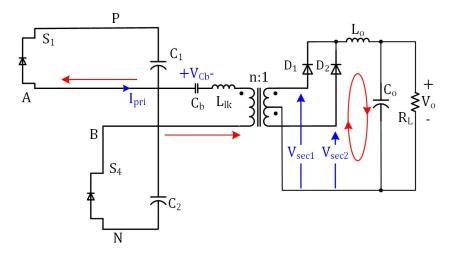

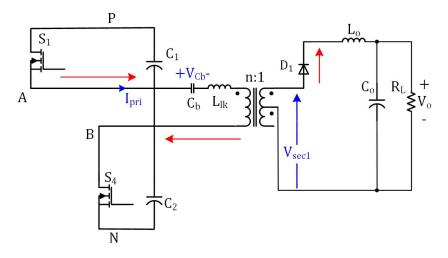

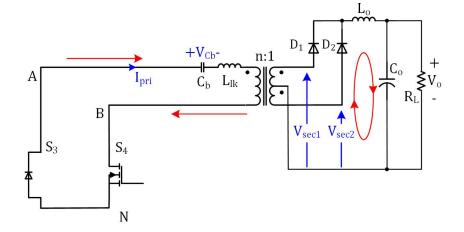

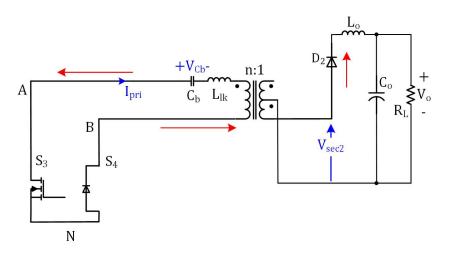

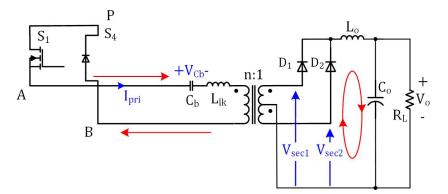

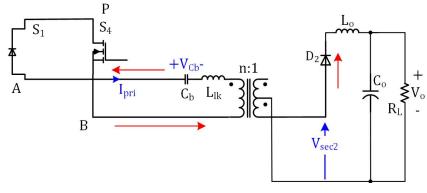

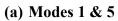

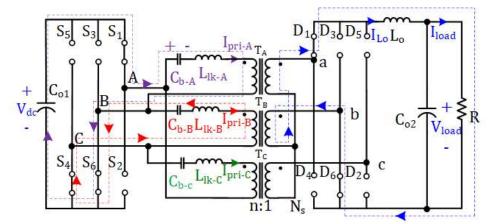

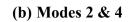

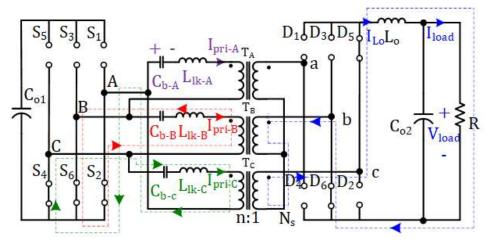

| Figure 4.6. Modes of operation                                                                                     | 82  |

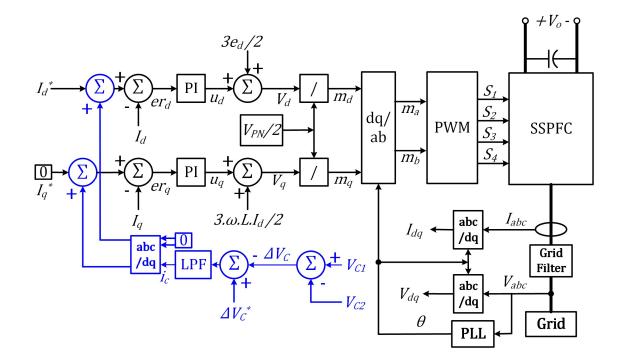

| Figure 4.7. Control system (voltage balancing control system is in blue)                                           | 84  |

| Figure 4.8. Output voltage variation with respect to the RL (x- axis) and transforme ratio (y-axis)                |     |

| Figure 4.9. Maximum DC bus voltage                                                                                 | 95  |

| Figure 4.10. The minimum value of L to achieve ZVS                                                                 |     |

| Figure 4.11. Simulated converter waveforms                                                                         | 101 |

| Figure 4.12. Typical converter waveforms                                                                           | 105 |

| Figure 4.13. Converter efficiency                                                                                  | 106 |

| Figure 5.1. A typical HMG                                                                                          | 108 |

| Figure 5.2. Simplified HMG 109                                                        |

|---------------------------------------------------------------------------------------|

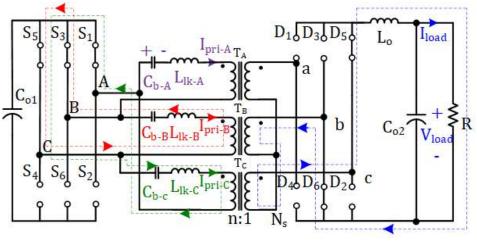

| Figure 5.3. Proposed MP-IC 111                                                        |

| Figure 5.4. Proposed MP-IC stages 112                                                 |

| Figure 5.5. Typical modulation signals 115                                            |

| Figure 5.6. Modes of operation of UDDSC 119                                           |

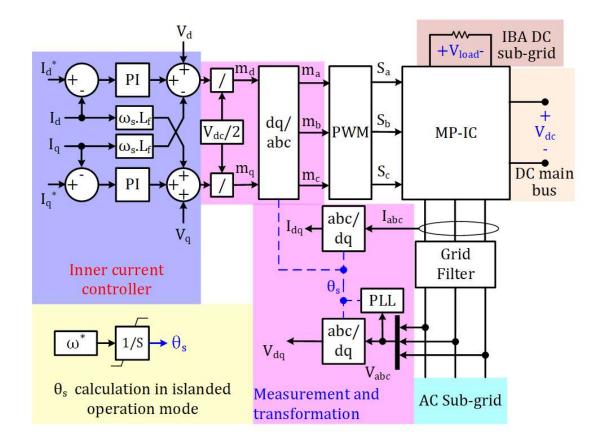

| Figure 5.7. Proposed MP-IC control system                                             |

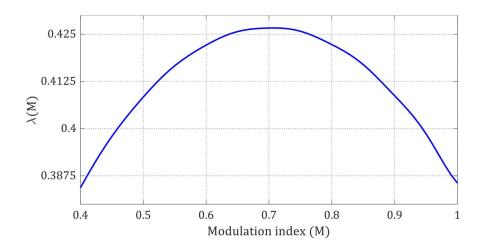

| Figure 5.8. $\lambda M$ variations vs. modulation index (M)                           |

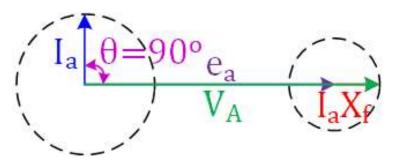

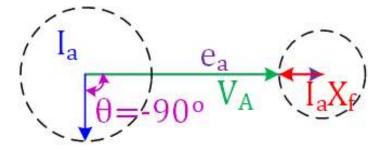

| Figure 5.9. Phasor diagram of the AC side of the MP-IC 125                            |

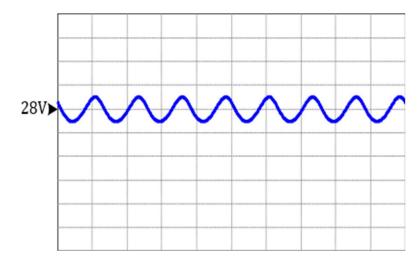

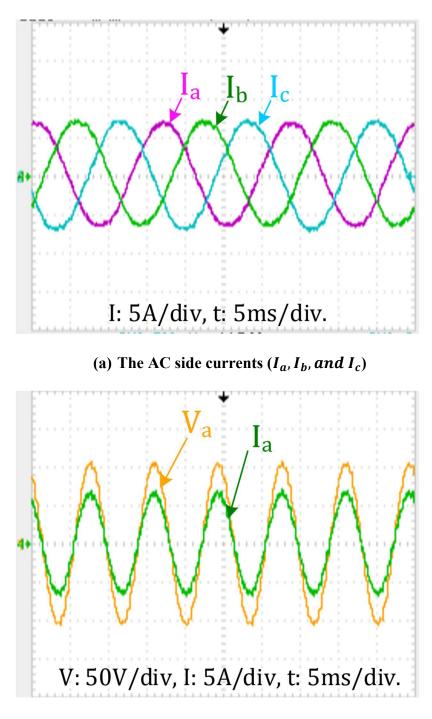

| Figure 5.10. Scaled-down prototype waveforms 129                                      |

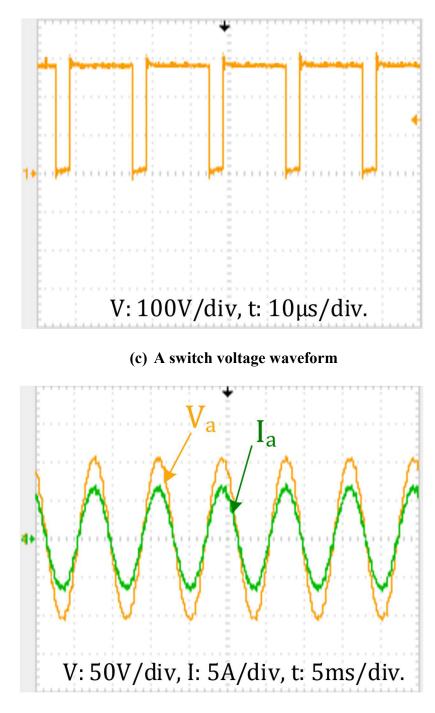

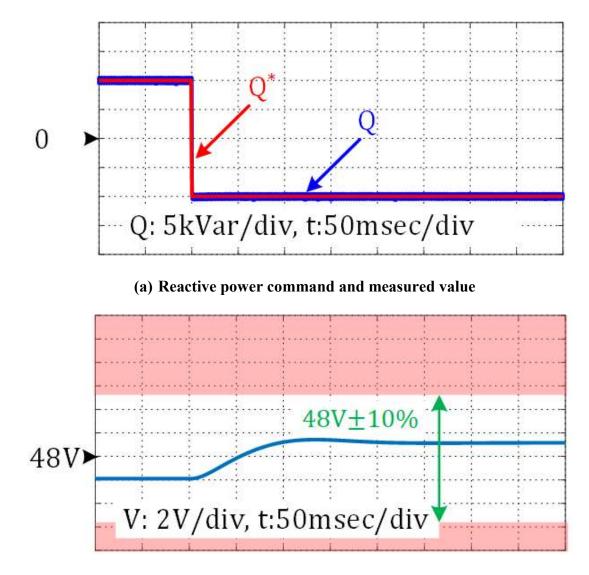

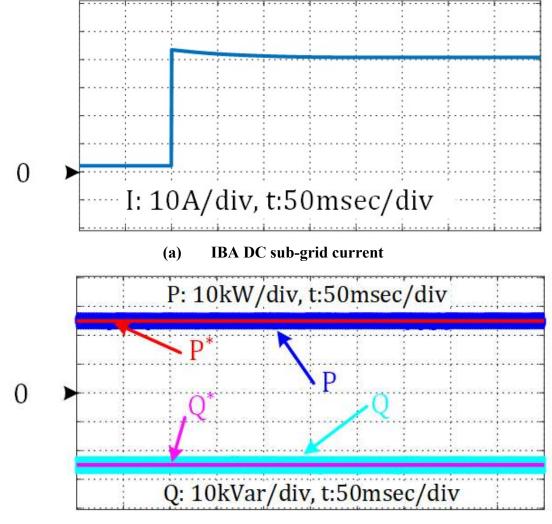

| Figure 5.11. IBA DC sub-grid voltage variations due to HMG operating point change 132 |

| Figure 5.12. The effect of IBA DC sub-grid load change on HMG operation               |

## Acronyms

| AC     | Alternate Current                           |

|--------|---------------------------------------------|

| DC     | Direct Current                              |

| ССМ    | Continuous Conduction Mode                  |

| DCM    | Discontinuous Conduction Mode               |

| EMI    | Electro-Magnetic Interference               |

| MOSFET | Metal Oxide Silicon Field Effect Transistor |

| PF     | Power Factor                                |

| PFC    | Power Factor Correction                     |

| PWM    | Pulse Width Modulation                      |

| RMS    | Root Mean Square                            |

| SSPFC  | Single-Stage Power Factor Correction        |

| TL     | Three Level                                 |

| THD    | Total Harmonic Distortion                   |

| ZCS    | Zero Current Switching                      |

| ZVS    | Zero Voltage Switching                      |

| ZVZCS  | Zero Voltage Zero Current Switching         |

#### Chapter 1

#### 1 Introduction

Power electronics is the application of solid-state electronics in electric circuit structures (topologies) to the control and conversion of electric power. Power electronic converters generally consist of semiconductor components such as MOSFETs, IGBTs, and diodes and passive components such as capacitors, inductors, and transformers. They are used to convert electric power from an existing power source to the form that is required by some load. Since electrical power can be either AC and DC, power electronic converters can be AC-AC, AC-DC, DC-AC, or DC-DC converters. The focus of the thesis is directed towards AC-DC and DC-DC converters with a split DC bus.

DC-DC converters are generally supplied from a DC source like a battery or they are supplied by a DC bus voltage that has been generated by a front-end AC-DC converter of some kind. It is a common practice in industry to implement AC-DC converters for switch-mode power supplies with two power stages – a front end AC-DC converter that converts input AC from the utility grid to an intermediate DC bus voltage that is then fed to a back-end isolated DC-DC converter that take this voltage and converts it to the required DC voltage needed to supply a load. In recent years, single-stage AC-DC converters that can perform the AC-DC conversion stage and the DC-DC converter stage AC-DC converter have become more popular as a way to reduce the cost of two-stage AC-DC converters. Regardless of whether an AC-DC converter has two converter stages or one, the converter has an intermediate DC bus.

In this thesis, AC-DC converters with a split DC bus will be examined. This split DC bus can be a bus that is implemented with two DC bus capacitors in series with each other, placed across the DC bus so that access to the midpoint voltage, which is half the bus voltage is available. A converter can also have a split DC bus with multiple current paths that allows multiple outputs to be fed by a single converter. The main advantages of implementing a converter with a split DC bus are either that its switches can be exposed

to lower voltages, which helps increase efficiency by reducing switching losses, or a converter stage can be removed, thus reducing cost and size.

In this thesis, the following topics will be examined:

- DC-DC converters with maximum power of 1 kW that are the back-end parts of two-stage AC-DC converters and that are fed from a split DC voltage bus.

- Single-stage AC-DC converters for switch-mode power supplies that have an intermediate DC voltage bus that is split.

- AC-DC interlinking converters for hybrid microgrids for information and communication technology (ICT) that can produce multiple DC voltages that can feed other parts of a microgrid.

In this chapter, a literature review of these topics will be performed, the thesis objectives will be stated, and the outline of the thesis will be given.

#### 1.1 DC-DC converters

DC-DC converters take an input DC voltage and convert it to another DC voltage that is typically less than the original DC voltage to supply a load or a set of loads of some kind. There are numerous DC-DC topologies that can be used in a variety of applications, but in general, it is the pulse-with modulated (PWM) full-bridge converter that is most often used for applications that are more than 500 W, especially when it is operated with phase-shift modulation to achieve zero-voltage switching (ZVS) in its switches. In this section, the operation of the PWM full-bridge is reviewed, its drawbacks are discussed, and a review of converters that have been previously proposed to overcome these drawbacks is performed.

#### 1.1.1 ZVS-PWM full-bridge converter

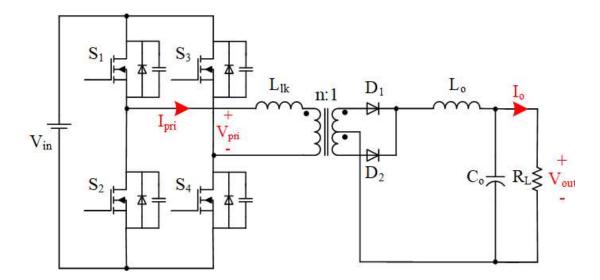

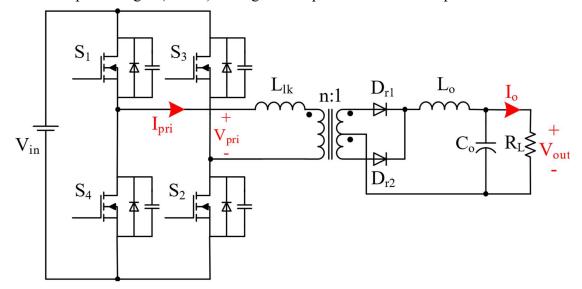

A circuit diagram of standard ZVS-PWM full-bridge (FB) converter is shown in Figure 1.1. The converter consists of four switches with internal anti-parallel body diodes, a transformer, two secondary output diodes, and an output filter that consists of an inductor

and a capacitor. The four converter switches convert a DC input voltage into a high-frequency (> 20 kHz) AC square waveform that is stepped down by the transformer, rectified by the secondary diodes, the filtered by the output LC filter to produce the DC voltage that is required by a load, represented as a resistor in Figure 1.1.

The converter works as follows: When a pair of diagonally opposed switches is on, the transformer primary winding is exposed to the input DC voltage. In this mode, the converter is in an energy-transfer mode and energy can be transferred from the transformer's primary to its secondary and then to the output. When two top switches ( $S_1$ ,  $S_3$ ) or two bottom switches ( $S_2$ ,  $S_4$ ) are on the converter works in the freewheeling mode as no voltage is impressed across the transformer primary and current in the converter's primary side and secondary side just circulates or freewheels, without result in any energy transfer. Each converter switch is on for about half of a periodic switching cycle, defined as half the time it takes for the converter to go through two energy-transfer modes (one for each pair of diagonally opposed switches) and two free-wheeling modes (one for the top pair of switches and one for the bottom pair).

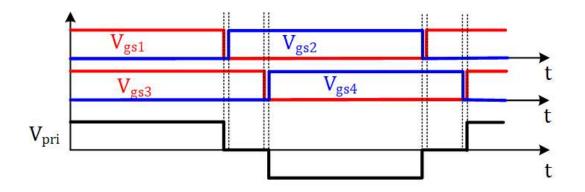

The gating signals that are needed to turn on the converter switches and the sequence by which they are turned on are shown in Figure 1.2. The width of the gating signal pulses never changes and the gating signal of a switch is complementary to that of the other

Figure 1.1. ZVS-PWM-FB DC-DC converter

Figure 1.2. ZVS-PWM-FB DC-DC converter typical waveforms

switch in the same leg so that the two switches of a converter leg are never on at the same time. The voltage that appears across the transformer primary, and thus the stepped-down transformer secondary, is dependent on the amount of overlap between diagonally opposed switches  $S_1$  and  $S_4$  and switches  $S_2$  and  $S_3$ , with voltage of one polarity placed across the transformer when  $S_1$  and  $S_4$  are on and voltage of the opposite polarity placed across the transformer when switch  $S_2$  and  $S_3$  are on. The converter's voltage is controlled by shifting the fixed-width signals of  $S_3$  and  $S_4$  relative to those of  $S_1$  and  $S_2$  so that the amount of time when diagonally opposed switches are on is increased or decreased. The signal for  $S_1$  is always the same relative to that of  $S_2$  and the signal of  $S_3$  is always the same relative to that of  $S_4$ .

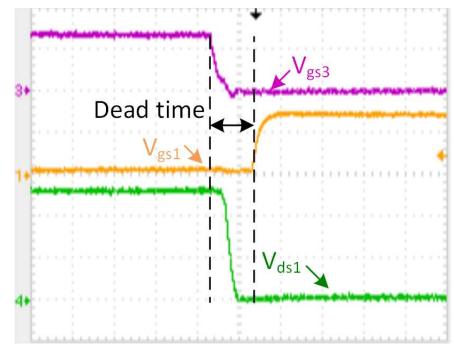

During each transition from an energy-transfer mode to a freewheeling mode and vice versa, there is a small amount of time (dead-time) when all switches are off. During this dead-time, energy stored in the leakage inductance of the converter's transformer (as a result of current circulating in the transformer's primary side) is used to discharge the parasitic capacitance of each switch before it is turned on, after its complementary switch in the same leg has been turned off. After this capacitance has been discharged, current can flow through the anti-parallel body-diode that is internal to each switching device so that the voltage across the switch can be clamped to near-zero voltage (one forward-voltage diode drop). With almost zero voltage across it, a switch can be turned on with zero voltage switching (ZVS). Operation with ZVS reduces power losses that can occur during a switching transition in a switch that would otherwise be caused by the overlap of

switch voltage and switch current, as shown in Figure 1.3. In the case where a switch is operating without ZVS,  $P_{on} = 1/2(V_s I_s)$  is dissipated in the switch. By making the voltage across a switch to be zero at the time of a turn-on transition, it can be turned on with ZVS. A switch's parasitic capacitance may be sufficient to slow down the rate of voltage rise when it is turned off, thus reducing the amount of overlap between voltage and current significantly. As a result, the switch can turn off with ZVS as well. Additional external capacitance can be added across a switching device if more capacitance is needed to slow down the rate of voltage rise further.

The ZVS-PWM converter has several drawbacks. The ones that will be examined in this these will be

- The converter has conduction power losses that are caused by current circulating in its primary whenever it is in a freewheeling mode of operation.

- The converter loses its ZVS capability when it is operating under light-load conditions as its switching losses increase.

## Figure 1.3. Power losses in a typical switch during turn-on process. (a) without ZVS, (b) with ZVS

These drawbacks are explained in detail in the next sections of this chapter.

#### 1.1.1.1 Circulating Current Losses

When the ZVS-PWM converter is in a freewheeling mode of operation, current flows through either  $S_1$  and  $S_3$  or  $S_2$  and  $S_4$ . For example, current can flow through S1 and the body-diode of  $S_3$ , or  $S_3$  and the body-diode of  $S_1$ , or  $S_2$  and the body-diode of  $S_4$ , or  $S_4$  and the body-diode of  $S_2$  during a freewheeling mode of operation. If the converter is implemented with MOSFETs, which allow current to flow in direction of source to drain through their switches instead of through their body-diodes, then current can flow through two switches during a freewheeling mode of operation.

The current flowing through two devices during a freewheeling mode of operation, creates conduction losses. These losses may be small when the converter is operating under full-load conditions but become more significant when the converter is operating under light-load conditions as (i) the converter operates more in freewheeling modes of operation, and (ii) conduction losses become larger relative to the amount of power delivered by the converter.

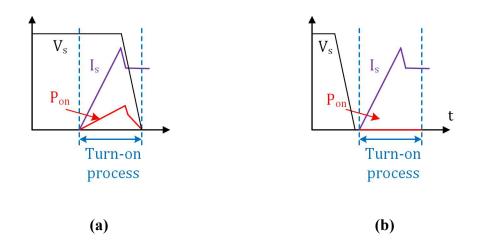

The main method that has been proposed to decrease the circulating current that appears in ZVS-PWM converters when they are operating in freewheeling modes of operation has been to modify their topologies to make them into zero-voltage-zero-current-switching (ZVZCS) converters [1]–[7]. An example of a ZVZCS-PWM full-bridge converter is shown in Figure 1.4. This converter is a ZVZCS converter because some of its switches operate with ZVS while some of its switches operate with ZCS.

Figure 1.4. ZVZCS-PWM-FB DC-DC converter

The basic principle behind ZVZCS converters like the one shown in Figure 1.4 is that when the converter is in a freewheeling mode of operation, a counter voltage of some kind is impressed across the secondary winding of the transformer, which is then reflected across the primary winding. The counter voltage is impressed across the secondary by means of auxiliary circuit capacitor Cc, which maintains its charge at the start of a freewheeling mode of operation and is then discharged sometime shortly afterwards. Without this counter voltage, current circulates in the converter's primary side and there is almost no voltage to oppose it and to force it down. With this counter voltage, however, the circulating current does encounter as opposing voltage that can force it down to almost zero, thus extinguishing it. As a result, conduction losses caused by freewheeling mode circulating current can be mostly eliminated.

The converter in Figure 1.4 is ZVZCS converter because the switching transitions that change the converter's mode of operation from an energy-transfer mode to a freewheeling mode of operation are ZVS while those that change the converter's mode of operation from a freewheeling mode to an energy-transfer mode are ZCS. The ZVS switching transitions are associated with the switches of one leg, while the ZCS transitions are associated with the switches of the other leg. For example, after circulating current has been extinguished in a freewheeling mode, one of the switch of the ZCS leg can be turned

off with ZCS as there is no current flowing through it while its complementary switch can be turned on with ZCS because the presence of transformer inductance in the primary current path limits the rate of current rise in the switch, which in turn limits the amount of overlap that exists between switch current and switch voltage during this switching transitions. As for the switches of the ZVS leg, they can operate with ZVS because the operation of the converter when it enters a freewheeling mode is identical to that of a standard ZVS-PWM full-bridge converter.

Although a number of ZVZCS-PWM full-bridge converters have been proposed, the main drawback that they have is that half of their four switches operate with ZVS while have their switches operate with ZCS. This means that either the converter is implemented with two MOSFET devices for the ZVS leg (as ZVS is preferable for MOSFETs) and two IGBT devices for the ZCS leg (as ZCS is preferable for IGBTs), which would raise the cost of the converter as multiple types of devices would be required instead of just one or the converter is implemented with IGBTs for all four switches even though two of the switches will need to operate ZVS. ZVZCS-PWM full-bridge converters are rarely, if ever, implemented with four MOSFETs as the MOSFET turn-on losses with no ZVS are significant and result in lower efficiency.

The conventional zero-voltage (ZVS), pulse width modulated (PWM) full-bridge (FB) DC-DC converter is widely used in industry in applications requiring DC-DC power conversion for loads greater than 500W [8]–[11]. This converter is popular because it is a PWM converter that has inherent ZVS operation when operating with heavy loads, as its switches can turn on with ZVS without the need for auxiliary circuitry. Although it is considered to be the standard converter for higher power applications where a four-switch topology is preferred over a one- or two-switch topology, it has a number of issues.

One of these is the fact that the switches of the converter lose their ZVS operating capability when it operates under light-load conditions. Although there is generally sufficient energy to discharge the output capacitances of switches that are turned on when the converter enters a freewheeling operation mode (when either two top switches or two bottom switches are on at the same time), there may not be enough energy to discharge

the output capacitances of switches that are turned on when the converter enters an energytransfer mode (when either pair of diagonally opposed switches are on at the same time). The main reason for the loss of ZVS in the latter case is that the only energy that is available to discharge the switch output capacitances is that stored in the primary-side leakage inductance of the converter's transformer. As the load is reduced, so too is the amount of this leakage inductance energy and a point is reached where the load is too low for there to be sufficient energy for the ZVS operation of the switches.

Using higher leakage inductance values allows the range of ZVS operation to be extended to a wider range of load variation, but at the cost of increasing duty cycle loss and power losses, thus decreasing converter efficiency for heavy- load operating conditions. As a result, there is a trade-off between leakage inductance and ZVS operation range that must be considered [12]–[15].

Another issue with the ZVS-PWM-FB converter is that when the converter is in a freewheeling mode of operation, current just circulates in the converter without any energy transferred to the secondary. This is because the voltage across the transformer primary is zero when either two top converter switches or two bottom converter switches are on so that the voltage across the transformer secondary is also zero. The circulating current flows through two converter devices and creates conduction losses. Converter switches are subjected to increased RMS current stresses as well for no beneficial reason [16]–[18].

A third issue is that although the control of the converter is simple PWM that regulates the output voltage by adjusting its duty cycle using phase-shift PWM [19], it can be a challenge to ensure that the transformer does not saturate. This can be done either by using sophisticated sensing methods to monitor the volt-seconds applied to a transformer during a switching period then making adjustments to balance the volt-seconds applied with either polarity across the transformer [5], [20], [21] or to put a DC blocking in series with the transformer [15]-[16], but each of these approaches has its own drawbacks.

As a result of these issues, power electronics researchers have proposed other four-switch topologies that offer improved performance to some degree such as increased ZVS

operating range and better light-load efficiency (e.g. [17]-[18]). Many of these alternative converters, however, are either very sophisticated or are simply variations of the conventional ZVS-PWM-FB converter with additional auxiliary circuitry added to the base four-switch topology and thus still have a number of the deficiencies of the ZVS-PWM-FB. Moreover, the addition of auxiliary circuitry adds to the overall cost of the converter.

#### 1.1.1.2 Light Load Efficiency

Power electronic converters are typically required to operate over a wide range of load conditions. Although this is the case, power converters tend to be designed to operate at load levels that are at least 50%-60% of full-load. It has only been in recent years that light-load efficiency has been a topic of concern, given the proliferation of power converters in society and the need to conserved energy from the grid.

ZVS-PWM full-bridge converters lose their ZVS capability when operating under lightload conditions because their transformer primary current is low and there is insufficient energy stored in their transformer leakage inductance that can discharge the parasitic capacitance of their switches so that they can be turned on while current is flowing in their body-diodes. There are several ways by which this drawback can be overcome, including the following:

- The turns ratio of the transformer can be decreased, which increases the amount of current that flows in the converter primary. Such an approach is rarely used, however, because this would increase converter conduction losses and switch turn-off losses as the converter switches would have to turn off higher amounts of current. As a result, the load threshold at which the converter switches cease to be able to operate with ZVS is typically set to be about 40%-50% of full-load as lowering this threshold introduces more losses than would be saved.

- An auxiliary circuit(s) that can generate more circulating current is added to the ZVS-PWM converter topology. Doing so, however, increases the cost of the converter as additional passive and/or active components are needed and also

introduces the same problems as decreasing the transformer turns ratio, though not to the same degree.

- The switching frequency of the converter can be changed when the converter is operating under light-load conditions so that the converter switches do not turn on and off as often as they do when it is operating under full-load conditions. Several converter control methods have been proposed to do this, but they are sophisticated and not easy to implement.

- A combination of the above methods can be used.

#### 1.1.2 Three-leg full-bridge converter

Circuit diagram of a three-leg ZVS-FB-PWM is shown in Figure 1.5. Thee leg ZVS-PWM-FB DC-DC converter. The converter operation principles are the same as the twoleg ZVS-FB-PWM converter. The only difference is using three legs, and more transformers reduce the stress on components that make the converter more desirable for high power applications.

#### 1.2 AC-DC converters

AC-DC converters convert an AC input voltage, which can be obtained from the utility grid or an AC generator, and convert it into a DC voltage that can be used to supply DC-

Figure 1.5. Thee leg ZVS-PWM-FB DC-DC converter

DC converters or DC-AC inverters. The input to AC-DC converters can be either singlephase AC or three-phase AC; the focus will be on three-phase AC-DC converters in this thesis.

It is standard practice to implement AC-DC converters with some sort of power factor correction (PFC) as their AC input side is connected to an AC voltage source and it is desired to draw sinusoidal current with a low harmonic content. Input AC current harmonics do not contribute to the power transfer from the AC input to the DC output and only create power losses and voltage distortion in the source, which is typically the grid. Total harmonic distortion (THD) and power factor (PF) are parameters that are associated with input current distortion and used to compare the performance of an AC-DC system. They are defined as [26]

$$PF = \frac{P}{S} \tag{1-1}$$

$$THD_I = \frac{\sqrt{I_2^2 + I_3^2 + I_4^2 + \cdots}}{I_1} \tag{1-2}$$

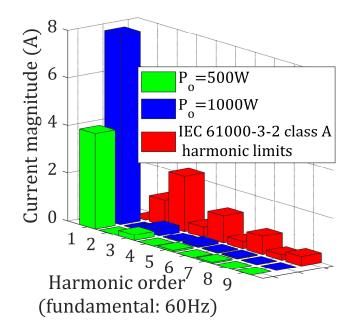

THD and PF are limited by regulatory standards such as IEC 61000-3-2[27], IEC 61000-3-4[28], and IEEE519[29] whenever an AC-DC converter is supplied from the utility grid.

#### 1.2.1 Two-stage isolated AC-DC converters

As stated in the Introduction to this chapter, AC-DC converters can be either two-stage converters with a front-end AC-DC converter followed by a back-end DC-DC converter or single-stage converters that can simultaneously perform AC-DC and DC-DC converter with just one converter. The standard implementation of a two-stage AC-DC converter with a three-phase AC input is shown in Figure 1.6. The back-end DC-DC converter in this figure is a ZVS-PWM DC-DC full-bridge converter; the front-end converter is a six-switch AC-DC converter that can be operated with PWM. Given that the converter has at least 10 switches, without including any auxiliary circuitry that may be added to improve performance, and that the PWM control of the front-end AC-DC converter can be complicated, researchers have tried to simplify the converter shown in Figure 1.6 by simplifying its topology and/or its control. Efforts to do so have focused on:

- simplifying just the front-end AC-DC converter and maintaining a two-stage topology,

- simplifying the overall converter by proposing alternative single-stage topologies,

- modifying the topology to simplify the control of the converter,

- implementing a combination of these methods.

Examples of modified AC-DC converters are reviewed in the next sections of this chapter.

Figure 1.6. circuit diagram of a typical two-stage isolated AC-DC converter

## 1.2.2 Front-end AC-DC converters for two-stage AC-DC converters

Approaches to simplifying the front-end AC-DC converter of a two-stage AC-DC converter have focused on reducing the number of switches that the front-end converter shown in Figure 1.6 has. Most of these approaches can be categorized as follows:

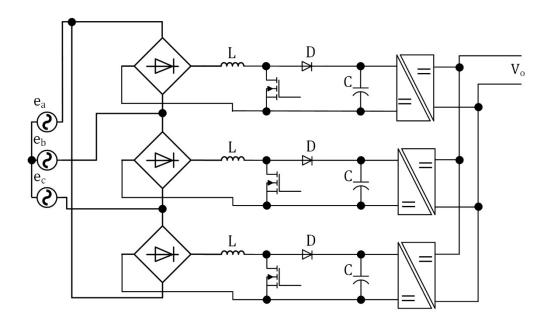

• Using three separate single-phase AC-DC boost converters as shown in Figure 1.8. Each boost converter module consists of a diode bridge, an input inductor, a

Figure 1.7. Isolate AC-DC converter proposed in [30]

switch, a diode, and a capacitor that acts as a filter. Each converter is implemented with a standard AC-DC boost converter topology or with a topology that is similar to it. Each module works as follows: The input inductor current rises when the switch is turned on and fall when the switch is turned off. By turning the switch on and off in an appropriate manner throughout the input AC line cycle, the input current of a module can be shaped to be sinusoidal and in phase with its input voltage. Each converter can be controlled individually, but its operation needs to be synchronized with the operation of the other modules. The advantages to this approach are that it only needs three active switches and that it is modular and thus can be implemented with commercially available single-phase AC-DC PFC converters. The main drawbacks are that it is expensive as any cost savings obtained from the elimination of three active switches are offset by the need for more passive components and that it can be challenging to synchronize the operation of all three modules, even through the use of sophisticated PWM schemes such as the ones needed to operate the six-switch front-end converter shown in Figure 1.6 are avoided [30].

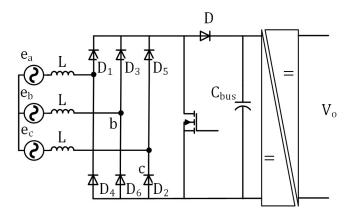

Using a single-switch three-phase converter such as the one shown in Figure 1.8 • that consists of a diode bridge, three input inductors, a switch, and an output capacitor that acts as an output filter [31]. The converter shown in Figure 1.8 is a boost-type converter, but three-phase single-switch converters have been developed from other topologies such as the buck, buck-boost and Cuk converters [32]–[37]. The converter shown in Figure 1.8 operates as follows: Current in all three input inductors rise when the switch is on and falls when the switch is off as energy is transferred to the output through the diode. If the input currents are discontinuous (i.e. are zero for part of a switching cycle) then they will take the shape of a series of triangular pulses with peaks that are bounded by the input voltage. These input current waveforms are essentially sinusoids with high frequency harmonics that can be filtered out. The advantages of single-switch three-phase converters are that they have a very simple topology and can be operated with very simple control methods - especially since the input current does not have to be monitored or sensed as input PFC can occur naturally as long

Figure 1.8. Isolate three-phase AC-DC converter with a boost DC-DC stage as the input currents are discontinuous. The main drawback is that is the converter switch is subjected to high current stresses as the peak current stress is high, since the input current is a set of triangular pulse with high current peaks, and AC-DC power conversion is performed with just one switch. This approach is generally limited to lower power applications where three-phase AC to DC conversion is needed.

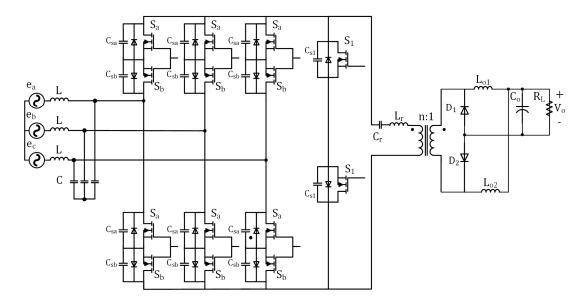

• Using a four-switch AC-DC converter as shown in Figure 1.9. This converter can be operated in the same manner as the six-switch front-end converter shown in Figure 1.6 and with the same PWM methods. It is possible to replace two of the switches in the six-switch converter with two capacitors and connect one of the phases to the midpoint of these capacitors instead of to the midpoint of a leg of switches[38], [39]. This is because in a three-phase system, if two of the input currents are controlled, then the third current is constrained so that it does not need to be actively controlled. The main advantage of this converter is that it does require fewer switches. The main drawbacks are that the switches have more stress than the switches in a six-switch converter, although the very high peak current stresses of single-switch three-phase AC-DC converters are avoided, and the control is sophisticated, like that of six-switch AC-DC converters. Moreover, when implemented in a two-stage AC-DC converter, the number of switches in the overall converter remains significant.

Figure 1.9. Isolate three-phase AC-DC converter by using the reduced switch converter proposed in [38]

#### 1.2.3 Single stage isolated three-phase AC-DC converters

The standard six-switch topology shown in Figure 1.6 can be further simplified if it is replaced by a single-stage topology. Generally, single-stage topologies fall into one of the following categories:

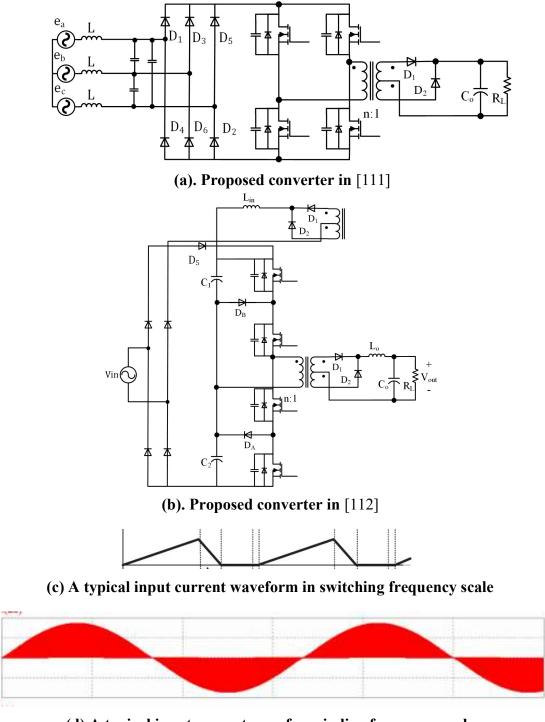

• They are synthesized by combining a single-switch front-end AC-DC converter with a DC-DC full-bridge converter, then removing any redundant components. An example of such a converter is shown in Figure 1.10. This can be done if the original AC-DC front-end converter is made to operate with the same fixed duty cycle as the DC-DC full-bridge converter as this introduces a redundancy in the overall converter that can be eliminated. Since redundant components can be eliminated, the control of the converter can be simplified as well as only one converter stage needs to be controlled instead of two. The main advantage of this approach is that three-phase AC-DC power conversion with isolation can be achieved with just four converter switches and with simple control, unless they are resonant topologies that are operated with a combination of variable-switching frequency control and pulse-width modulation (PWM) [40], [41]. The main drawbacks are that the input currents consist of triangular pulses with high peaks

that are bounded by a sinusoidal envelope, which increases the peak current stress of the converter switches, the converter switches may have to conduct current resulting from both the AC-DC conversion process and the DC-DC conversion process, which increases current stresses, and, if there is an intermediate DC bus voltage, this voltage may become high as it is not regulated since the converter operates with just a single controller that is used to regulate the output voltage. Single-stage converters of this type are generally used for lower power applications.

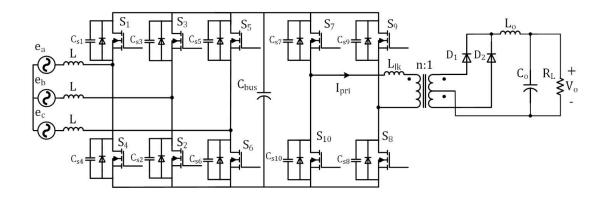

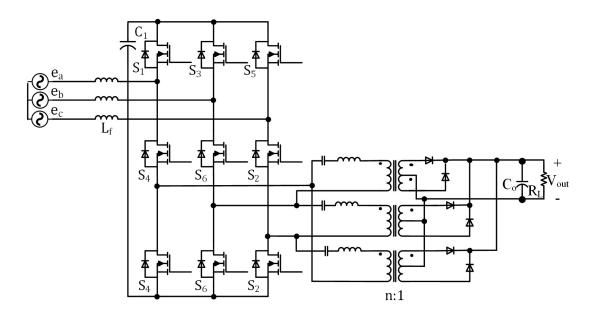

• They still require a significant number of switches, especially when so-called matrix-type topologies, which can require at least six pairs of back-to-back switches (12 switches in total) like the converter shown in Figure 1.11 is used [41]–[43]. In the case of matrix converters such as the one shown in Figure 1.11, power conversion is performed by applying bits and pieces of rectified three-phase AC voltage across the transformer in an appropriate manner. The main advantage of matrix converters is that they are generally more efficient than two-stage converters as power is only processed once by the converter instead of twice by the two stage of a two-stage converter. Moreover, they do not have an input diode bridge that can contribute to conduction losses The main drawback is that the control of these converters can be very sophisticated and the number of converter switches are still significant [44]–[46]. Single-stage converters of this type are generally used for higher power applications.

(d) A typical input current waveform in line frequency scale

Figure 1.10. Single stage AC-DC converters and their associated waveforms

(a) Proposed converter in [42]

**(b) Proposed converter in** [43]

Figure 1.11. Single stage AC-DC converters

#### 1.3 Hybrid AC-DC Microgrids

The use of distributed generation (DG) units in power systems is becoming more popular as they are green, flexible and economical. DGs are connected to the power grid through a power electronic converter, but they are intermittent sources of energy, which creates issues related to system stability, reliability, and power quality. Microgrids (MGs) have been developed to address some of these issues. They are independently operated clusters of small DGs, storage units and loads that can be run either as a stand-alone system (islanded MG) or be connected to a bulk power grid (grid-connected MG), which is more common as this results in higher reliability. MGs increase the resource utilization of small DGs, the resilience of power systems, and the flexibility of system design [1]-[2].

Grid-connected MGs are typically AC MGs (as opposed to DC MGs) since the bulk power system that they are connected to is an AC system. AC MGs, however, have several issues that are related to reactive power, synchronization, and power quality so that the popularity of DC MGs has been increasing as they do not have these issues [49]. Moreover, DC MGs are more efficient than AC MGs as most DG units, energy storage elements, and load work with DC voltage, thus most power conversion losses from AC to DC and vice versa are eliminated [50]. Nonetheless, DC MGs still need to be implemented with AC-DC and DC-AC power converters because they need to be connected to a bulk power AC system to be reliable and some of their DG units and loads require AC voltage to operate and need to be interfaced to DC MGs with power converters.

Hybrid AC-DC MGs (HMGs), which were introduced in [51], combine the advantages of both AC and DC MGs. HMGs consists of two separate sub-grids: an AC sub-grid that is connected to the bulk power system, AC DGs, and loads, and a. DC sub-grid that is connected to DC DGs, energy storage elements, and DC loads. HMGs are more efficient than pure AC or DC MGs because both the AC and DC loads and the DG units are connected to AC and DC sub-grids directly.

In an HMG, both the AC and DC sub-grids can be operated as two separate MGs, with a a unified control strategy that allows power to be transferred between AC and DC subgrids, which allows AC and DC resources to be managed in a way that makes the operation of the HMG more efficient and reliable [52]–[57]. This power transfer can be achieved by a bidirectional AC-DC converter that allows power to flow from AC to DC sub-grid and vice versa. This converter is commonly referred to as an interlinking converter (IC) in the literature and is a required element in any HMG, regardless of the complexity of HMG structure. HMG control and operation strategies are designed to optimize the overall system operation and use of AC and DC sub-grid resources, and the output command of the control system is often executed by the IC [51], [58]–[61].

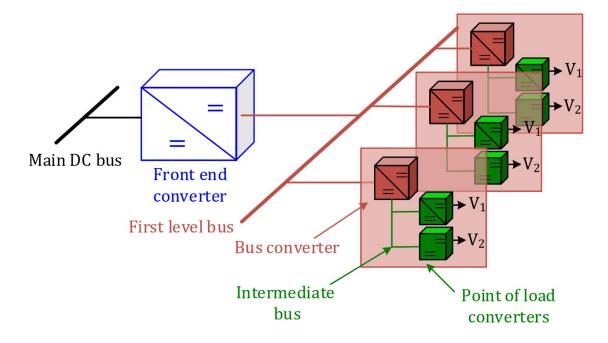

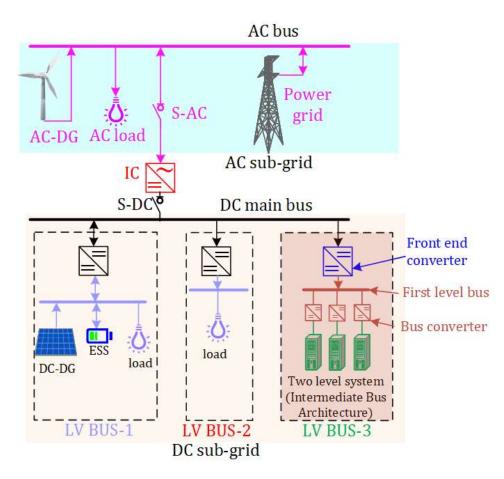

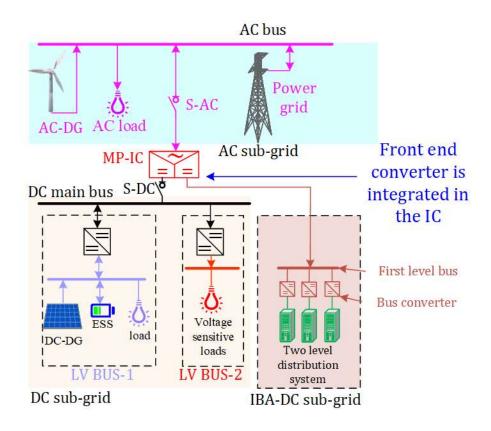

A typical HMG with an AC and a DC sub-grid is shown in Fig. 1. The AC sub-grid consists of an AC bus that is connected to an AC power grid, a typical AC-DG unit, and a lumped AC load that models all AC loads. The DC sub-grid consists of three smaller, generic DC sub-grids that are connected to a common DC main bus. LV BUS-1 models a composite DC sub-grid that consists of a DC DG unit, an energy storage system (ESS), and a lumped load. LV BUS-1 is connected to the main DC bus through a bidirectional DC-DC converter and it injects surplus power or absorbs needed power from the main DC bus. LV BUS-2 models a cluster of DC small DC loads (< 2 kW) that are sensitive to voltage variations such as LEDs. LV BUS-3 models a group of large DC loads (> 2 kW) and has a two level distribution system architecture, which is referred to as an Intermediate Bus Architecture (IBA) in the literature; the IBA is shown in more detail in shown in Fig. 2. The IBA decreases the overall system cost and increases the overall system efficiency for large DC distribution systems (> 2 kW) [62].

In a DC distribution system with an IBA, a front-end converter steps down the main DC bus voltage to the first-level bus voltage and provides galvanic isolation. The first-level bus voltage can be either a semi-regulated DC voltage (i.e.  $48V\pm10\%$ ) or a wide range variation voltage (i.e. 36V-75V). Power is distributed among the loads attached to the first-level bus, and a bus converter is used to convert the first-level bus voltage to a regulated secondary bus voltage that is used to supply point-of-load (POL) converters for each load [62]–[65].

In a typical HMG such as the one shown in Fig. 1, a significant number of power electronic converters is needed to supply the DC loads at different voltage levels. This neutralizes

Figure 1.12. DC system with Intermediate Bus Architecture (IBA) [62]

one of the advantages of using HMG, which is that they require fewer power electronic converters than AC MGs or DC MGs. This issue can be addressed by using multi-port converters in an HMG to simplify its HMG architecture and reduce its overall size and cost. Few such converters have been proposed, however, and the ones that have been proposed have at least one of the following disadvantages:

- They need a considerable number of switches as they are interfacing more than one DC bus to three phase systems [66]–[68].

- They need to be operated with very sophisticated control methods so that they can perform AC-DC and DC-DC conversion simultaneously [69]–[71].

# 1.4 Thesis Objectives

Split DC bus converters are proposed in this thesis to reduce the size and cost of power electronic converters and to improve efficiency. The number of active switches in these converters can be fewer than that of conventional topologies, and/or these switches may be subjected to less voltage stress. The converters presented in this thesis are either completely original or are modified versions of existing topologies.

The main objectives of this thesis are as follows:

- To evaluate the application of split DC bus DC-DC converters as a way of improving light-load efficiency in four-switch PWM full-bridge type converters.

- To evaluate the application of split DC bus DC-DC converters as a way of reducing conduction losses created by freewheeling mode circulating current in four-switch PWM full-bridge type converters.

- To propose a new single-stage AC-DC bridgeless converter with a split DC bus configuration that has galvanic isolation, continuous input current for lower peak stress, and a minimal number of switches.

- To propose a new split DC bus converter that can be used to simplify HMG structures.

- To determine the steady-state characteristics of the new converters proposed in the thesis to derive appropriate design procedures.

- To confirm the feasibility of the proposed converters and the validity of theoretical concept in this thesis with experimental results obtained from proof-of-concept prototypes and simulation results obtained for HMGs.

# 1.5 Thesis Outline

The thesis consists of the following six chapters. Following is a brief explanation of each chapter.

The focus of chapter 2 is to investigate the properties of a type split DC bus DC-DC converter. This chapter investigates two features of the split DC bus DC-DC converter, including less stress of the switches and reducing circulating current and how these features can be used to improve the DC-DC converter performance.

In Chapter 2, the use of three-level (TL), zero-voltage-zero-current switching (ZVZCS) converters is investigated as a way of improving light-load efficiency in full-bridge

converters with MOSFETS. TL-ZVZCS full-bridge converters are split DC bus converters that are used in high-voltage, high-power applications with IGBT devices, but their use in lower voltage, lower power applications where MOSFETs are generally used has not been investigated. In this chapter, the general operation of an example TL-ZVZCS full-bridge converter is briefly explained and the basic principles as to how it can how improve light-load efficiency are discussed. Experimental results that compare the efficiency of a prototype of the example TL-ZVZCS converter to that of the conventional ZVS-PWM full-bridge and a two-level ZVZCS-PWM converter are presented as well.

In Chapter 3, the operation of the ZVS T-type DC-DC converter, a converter with a split DC bus that has been proposed as an alternative to the conventional ZVS-PWM fullbridge (FB) converter, is reviewed. Although it has a number of advantageous features, the ZVS T-type DC-DC converter is not well known among power electronic engineers working with switch-mode power supplies, and the topology has thus been neglected. In this chapter, the operation of the DC-DC ZVS T-type converter is contrasted to that of the conventional ZVS-PWM-FB DC-DC converter for lower power applications. Results obtained from prototypes of each converter topology are then presented, compared, and discussed, and conclusions which converter is superior for particular applications are made.

In Chapter 4, a new single-stage three-phase AC-DC converter with four switches and galvanic isolation is proposed. The new converter is simple and uses fewer switches than previously proposed AC-DC converters of the same type. It is a bridgeless converter that can operate with continuous input current and with any PWM method suitable for a standard three-phase six-switch voltage source rectifier. In this chapter, the operation, control, analysis and design of the proposed converter are explained and its features are discussed. Experimental results obtained from a prototype that confirm the feasibility of the converter are presented as well.

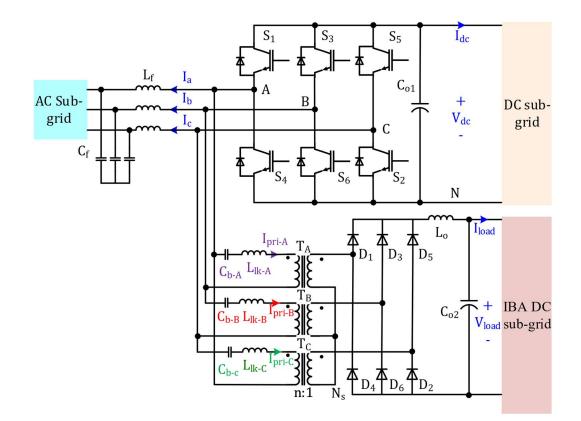

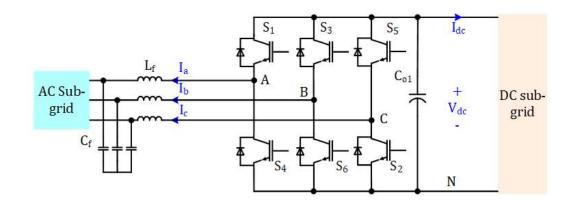

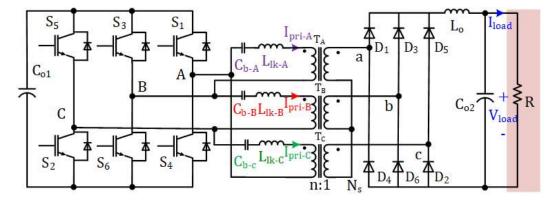

In Chapter 5, a new split DC bus converter that can be used as an interlinking converter for HMGs is proposed. The new converter, which can be implemented with only 6 active switches and any control method that can be used for conventional six-switch three-phase

AC-DC converters, can replace two converters in HMGs, thus simplifying their structure and reducing their cost. The converter can interface an AC system to a high voltage DC system as a bidirectional converter and to a low voltage isolated DC system as a unidirectional converter. The operation of the novel converter is discussed in detail, and the steady-state converter model is determined. The converter's design procedure is explained and demonstrated with a design example, and feasibility of the proposed converter is confirmed with experimental results from a proof-of-concept prototype, and its operation in a HMG is confirmed with simulation results.

In Chapter 6, the contents of this thesis are summarized, the contributions of this thesis are stated as are suggestions for future work.

# Chapter 2

# 2 Using Multilevel ZVZCS Converters to Improve Light-Load Efficiency in Low Power Applications

# 2.1 Introduction

The standard ZVS-PWM DC-DC full-bridge converter implemented with MOSFETS as shown in Figure 2.1 is widely used in applications with loads  $\geq$  500W. Its MOSFET switches can operate with ZVS if inductive energy stored in the transformer leakage inductance (L<sub>lk</sub>) is used to discharge their output capacitances before they are turned on [72]. When the converter is operating with light loads, however, this energy is not enough and so the switches turn on with switching losses, which results in poor efficiency for light loads. Such efficiency is becoming less acceptable as ever-increasing demands for power are placed on the utility grid to satisfy consumer demands.

In this chapter, the use of three-level (TL), zero-voltage-zero-current switching (ZVZCS) converter topologies that are implemented with IGBTs and that are typically operated at higher power levels (> 1 kW) with high DC input bus voltages (> 800 V) is investigated as a way of improving light-load efficiency in lower power full-bridge PWM converters (< 1 kW) that are implemented with MOSFETs and operated with lower, more standard DC bus input voltages (400 V). The general operation of an example TL-ZVZCS full-

Figure 2.1. FB-ZVS-PWM DC-DC converter

bridge converter is briefly explained in this chapter and the basic principles as to how it can how improve light-load efficiency are discussed. Experimental results that compare the efficiency of a prototype of the example TL-ZVZCS converter to that of the conventional ZVS-PWM full-bridge are presented to confirm the superior light-load efficiency of TL-ZVZCS converters.

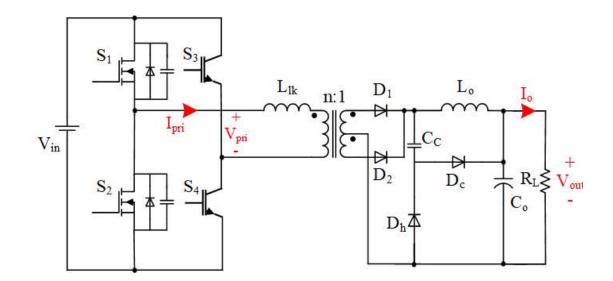

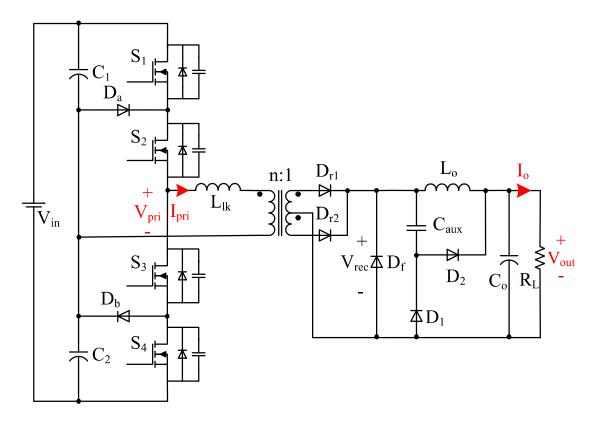

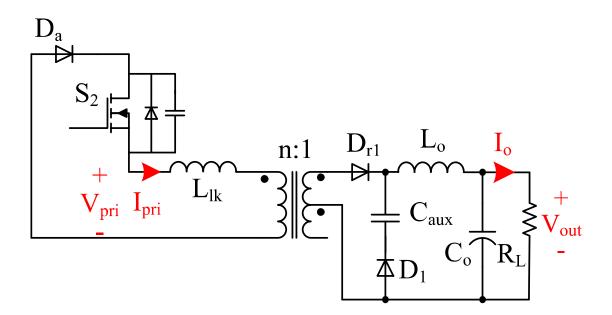

# 2.2 Example TL-ZVZCS DC-DC converter operation

A number of TL-ZVZCS DC-DC converters have been proposed in the literature [7], [73], [74]. The example TL-ZVZCS converter that was used for this study is shown in Figure 2.2; it was selected because it is among the simplest of its type. It is a standard three-level DC-DC converter with a secondary auxiliary circuit that consists of  $C_{aux}$ ,  $D_1$ ,  $D_2$  and  $D_f$ . Since the operation of the standard three-level DC-DC converter is well-known and can be found in the literature (i.e. [75], [76]), it is only briefly summarized in this section. Only the operation of the secondary auxiliary circuit is discussed in detail.