**Electronic Thesis and Dissertation Repository**

3-24-2017 12:00 AM

# MetaFork: A Compilation Framework for Concurrency Models Targeting Hardware Accelerators

Xiaohui Chen, The University of Western Ontario

Supervisor: Marc Moreno Maza, *The University of Western Ontario*A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Computer Science

© Xiaohui Chen 2017

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Algebra Commons, Computer and Systems Architecture Commons, Programming Languages and Compilers Commons, and the Software Engineering Commons

#### **Recommended Citation**

Chen, Xiaohui, "MetaFork: A Compilation Framework for Concurrency Models Targeting Hardware Accelerators" (2017). *Electronic Thesis and Dissertation Repository*. 4429. https://ir.lib.uwo.ca/etd/4429

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

#### **Abstract**

Parallel programming is gaining ground in various domains due to the tremendous computational power that it brings; however, it also requires a substantial *code crafting* effort to achieve performance improvement. Unfortunately, in most cases, performance tuning has to be accomplished manually by programmers. We argue that automated tuning is necessary due to the combination of the following factors. First, code optimization is machine-dependent. That is, optimization preferred on one machine may be not suitable for another machine. Second, as the possible optimization search space increases, manually finding an optimized configuration is hard. Therefore, developing new compiler techniques for optimizing applications is of considerable interest.

This thesis aims at generating new techniques that will help programmers develop efficient algorithms and code targeting hardware acceleration technologies, in a more effective manner. Our work is organized around a compilation framework, called Metafork, for concurrency platforms and its application to automatic parallelization. Metafork is a high-level programming language extending C/C++, which combines several models of concurrency including fork-join, SIMD and pipelining parallelism. Metafork is also a compilation framework which aims at facilitating the design and implementation of concurrent programs through four key features which make Metafork unique and novel:

- (1) Perform automatic code translation between concurrency platforms targeting multi-core architectures.

- (2) Provide a high-level language for expressing concurrency as in the fork-join model, the SIMD paradigm and the pipelining parallelism.

- (3) Generate parallel code from serial code with an emphasis on code depending on machine or program parameters (e.g. cache size, number of processors, number of threads per thread block).

- (4) Optimize code depending on parameters that are unknown at compile-time.

**Keywords:** source-to-source compiler, pipelining, comprehensive parametric CUDA kernel generation, concurrency platforms, high-level parallel programming.

### Acknowledgments

The work discussed in this dissertation would not have been possible without the constant encouragement and insight of many people.

I must express my deepest appreciation and thanks to my supervisor Professor Marc Moreno Maza, for his enthusiasm and patience during the course of my PhD research. I also would like to thank my friends Ning Xie, Changbo Chen, Yuzhen Xie, Robert Moir and Colin Costello in University of Western Ontario. My appreciation also goes to my IBM colleagues in compiler group, Wang Chen, Abdoul-Kader Keita, Priya Unnikrishnan and Jeeva Paudel, for their discussions on developing compiler techniques.

Many thanks to the members of my supervisory committee Professor John Barron and Professor Michael Bauer for their valuable feedbacks. Also my sincere thanks and appreciation go to the members of my examination committee Professor Robert Mercer, Professor Robert Webber, Professor David Jeffrey and Professor Jeremy Johnson for their comments and inspiration.

Last but not the least, I am also greatly indebted to my family who deserves too many thanks to fit this page.

# **Contents**

| Al | bstrac  | et            |                                                              | ii  |

|----|---------|---------------|--------------------------------------------------------------|-----|

| A  | cknov   | vledgme       | ents                                                         | iii |

| Li | st of l | Figures       |                                                              | vii |

| Li | st of ' | <b>Fables</b> |                                                              | xi  |

| Li | st of A | Append        | ices                                                         | xii |

| 1  | Intr    | oductio       | n                                                            | 1   |

|    | 1.1     | Disser        | tation Outline                                               | 2   |

|    | 1.2     | Contri        | butions                                                      | 3   |

|    | 1.3     | Thesis        | Statement                                                    | 3   |

| 2  | Bacl    | kground       | d                                                            | 4   |

|    | 2.1     | _             | rrency Platforms                                             | 4   |

|    |         | 2.1.1         | CILKPLUS                                                     | 4   |

|    |         | 2.1.2         | OpenMP                                                       | 5   |

|    |         | 2.1.3         | GPU                                                          | 5   |

|    | 2.2     | Perform       | mance Measurement                                            | 7   |

|    |         | 2.2.1         | Occupancy and ILP                                            | 8   |

|    |         | 2.2.2         | Work-Span Model                                              | 9   |

|    |         | 2.2.3         | Master Theorem                                               | 9   |

|    | 2.3     | Compi         | ilation Theory                                               | 10  |

|    |         | 2.3.1         | The State of the Art of Compilers                            | 10  |

|    |         | 2.3.2         | Source-to-Source Compiler                                    | 11  |

|    |         | 2.3.3         | Automatic Parallelization                                    | 12  |

| 3  | A M     | letalang      | guage for Concurrency Platforms Based on the Fork-Join Model | 13  |

|    | 3.1     | _             | Principles and Execution Model                               | 14  |

|    | 3.2     |               | Parallel Constructs                                          | 14  |

|    | 3.3     |               | le Attribute Rules                                           | 18  |

|    | 3.4     |               | ntics of the Parallel Constructs in MetaFork                 | 20  |

|    | 3.5     | Suppor        | rted Parallel APIs of Both CilkPlus and OpenMP               | 21  |

|    |         | 3.5.1         | OpenMP                                                       |     |

|    |         | 3.5.2         | CirkPrus                                                     | 26  |

|   |     | Translation                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                     |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   |     | 3.6.1 Translation from CILKPLUS to METAFORK                                                                                                                                                                                                                                                                                                                                                                                   | 28                                     |

|   |     | 3.6.2 Translation from MetaFork to CilkPlus                                                                                                                                                                                                                                                                                                                                                                                   | 29                                     |

|   |     | 3.6.3 Translation from OpenMP to MetaFork                                                                                                                                                                                                                                                                                                                                                                                     | 31                                     |

|   |     | 3.6.4 Translation from MetaFork to OpenMP                                                                                                                                                                                                                                                                                                                                                                                     | 39                                     |

|   | 3.7 | Experimentation                                                                                                                                                                                                                                                                                                                                                                                                               | 39                                     |

|   |     | 3.7.1 Experimentation Setup                                                                                                                                                                                                                                                                                                                                                                                                   | 41                                     |

|   |     | 3.7.2 Correctness                                                                                                                                                                                                                                                                                                                                                                                                             | 42                                     |

|   |     | 3.7.3 Comparative Implementation                                                                                                                                                                                                                                                                                                                                                                                              | 42                                     |

|   |     | 3.7.4 Interoperability                                                                                                                                                                                                                                                                                                                                                                                                        | 43                                     |

|   |     | 3.7.5 Parallelism Overheads                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                     |

|   | 3.8 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                     |

| 4 | App | olying MetaFork to the Generation of Parametric CUDA Kernels                                                                                                                                                                                                                                                                                                                                                                  | 52                                     |

|   | 4.1 | Optimizing CUDA Kernels Depending on Program Parameters                                                                                                                                                                                                                                                                                                                                                                       | 53                                     |

|   | 4.2 | Automatic Generation of Parametric CUDA Kernels                                                                                                                                                                                                                                                                                                                                                                               | 55                                     |

|   | 4.3 | Extending the MetaFork Language to Support Device Constructs                                                                                                                                                                                                                                                                                                                                                                  | 57                                     |

|   | 4.4 | The MetaFork Generator of Parametric CUDA Kernels                                                                                                                                                                                                                                                                                                                                                                             | 61                                     |

|   | 4.5 | Experimentation                                                                                                                                                                                                                                                                                                                                                                                                               | 64                                     |

|   | 4.6 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                                     |

| 5 | Мет | FAFORK: A Metalanguage for Concurrency Platforms Targeting Pipelining                                                                                                                                                                                                                                                                                                                                                         | 74                                     |

|   | 5.1 | Execution Model of Pipelining                                                                                                                                                                                                                                                                                                                                                                                                 | 74                                     |

|   | 5.2 | Core Parallel Constructs                                                                                                                                                                                                                                                                                                                                                                                                      | 75                                     |

|   | 5.3 | Semantics of the Pipelining Constructs in MetaFork                                                                                                                                                                                                                                                                                                                                                                            | 77                                     |

|   | 5.4 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                     |

| 6 | Мет | TAFORK: The Compilation Framework                                                                                                                                                                                                                                                                                                                                                                                             | <b>79</b>                              |

|   | 6.1 | Goals                                                                                                                                                                                                                                                                                                                                                                                                                         | 79                                     |

|   | 6.2 | МетаFork as a High-Level Parallel Programming Language                                                                                                                                                                                                                                                                                                                                                                        | 81                                     |

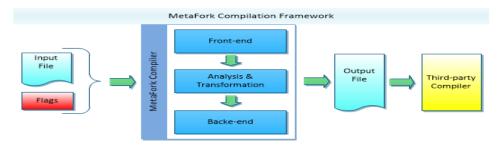

|   | 6.3 | Organization of the MetaFork Compilation Framework                                                                                                                                                                                                                                                                                                                                                                            | 83                                     |

|   | 6.4 | MetaFork Compiler                                                                                                                                                                                                                                                                                                                                                                                                             | 83                                     |

|   |     | 6.4.1 Front-End of the MetaFork Compiler                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                               | 84                                     |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                               | 84<br>85                               |

|   |     | 6.4.2 Analysis & Transformation of the МетаFork Compiler                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|   | 6.5 | 6.4.2 Analysis & Transformation of the МетаFork Compiler                                                                                                                                                                                                                                                                                                                                                                      | 85<br>87                               |

|   | 6.5 | 6.4.2 Analysis & Transformation of the МетаFork Compiler                                                                                                                                                                                                                                                                                                                                                                      | 85<br>87<br>87                         |

|   | 6.5 | 6.4.2 Analysis & Transformation of the МетаFork Compiler                                                                                                                                                                                                                                                                                                                                                                      | 85<br>87<br>87<br>88                   |

|   | 6.5 | <ul> <li>6.4.2 Analysis &amp; Transformation of the ΜεταFork Compiler</li> <li>6.4.3 Back-End of the ΜεταFork Compiler</li> <li>User Defined Pragma Directives in ΜεταFork</li> <li>6.5.1 Registration of Pragma Directives in the ΜεταFork Preprocessor</li> <li>6.5.2 Parsing of Pragma Directives in the ΜεταFork Front-End</li> </ul>                                                                                     | 85<br>87<br>87<br>88<br>89             |

|   |     | 6.4.2 Analysis & Transformation of the MetaFork Compiler                                                                                                                                                                                                                                                                                                                                                                      | 85<br>87<br>87<br>88<br>89<br>90       |

|   | 6.5 | <ul> <li>6.4.2 Analysis &amp; Transformation of the ΜΕΤΑFORK Compiler</li> <li>6.4.3 Back-End of the ΜΕΤΑFORK Compiler</li> <li>User Defined Pragma Directives in ΜΕΤΑFORK</li> <li>6.5.1 Registration of Pragma Directives in the ΜΕΤΑFORK Preprocessor</li> <li>6.5.2 Parsing of Pragma Directives in the ΜΕΤΑFORK Front-End</li> <li>6.5.3 Attaching Pragma Directives to the CLANG AST</li> <li>Implementation</li> </ul> | 85<br>87<br>87<br>88<br>89<br>90       |

|   |     | 6.4.2 Analysis & Transformation of the Мета Fork Compiler                                                                                                                                                                                                                                                                                                                                                                     | 85<br>87<br>87<br>88<br>89<br>90<br>90 |

|   |     | <ul> <li>6.4.2 Analysis &amp; Transformation of the ΜΕΤΑFORK Compiler</li> <li>6.4.3 Back-End of the ΜΕΤΑFORK Compiler</li> <li>User Defined Pragma Directives in ΜΕΤΑFORK</li> <li>6.5.1 Registration of Pragma Directives in the ΜΕΤΑFORK Preprocessor</li> <li>6.5.2 Parsing of Pragma Directives in the ΜΕΤΑFORK Front-End</li> <li>6.5.3 Attaching Pragma Directives to the CLANG AST</li> <li>Implementation</li> </ul> | 85<br>87<br>87<br>88<br>89<br>90       |

|    | 7.1                 | Comprehensive Optimization                                            | 102 |

|----|---------------------|-----------------------------------------------------------------------|-----|

|    |                     | 7.1.1 Hypotheses on the Input Code Fragment                           | 102 |

|    |                     | 7.1.2 Hardware Resource Limits and Performance Measures               | 103 |

|    |                     | 7.1.3 Evaluation of Resource and Performance Counters                 | 104 |

|    |                     | 7.1.4 Optimization Strategies                                         | 105 |

|    |                     | 7.1.5 Comprehensive Optimization                                      | 105 |

|    |                     | 7.1.6 Data-Structures                                                 | 106 |

|    |                     | 7.1.7 The Algorithm                                                   | 107 |

|    | 7.2                 | Comprehensive Translation of an Annotated C Program into CUDA Kernels | 112 |

|    |                     | 7.2.1 Input MetaFork Code Fragment                                    | 112 |

|    |                     | 7.2.2 Comprehensive Translation into Parametric CUDA Kernels          | 113 |

|    | 7.3                 | Implementation Details                                                | 114 |

|    | 7.4                 | Experimentation                                                       | 116 |

|    | 7.5                 | Conclusion                                                            | 122 |

| 3  | Con                 | ncluding Remarks                                                      | 126 |

| Bi | Bibliography        |                                                                       |     |

| 4  | Cod                 | le Translation Examples                                               | 141 |

| В  | Exa                 | amples Generated by PPCG                                              | 153 |

| С  | The                 | Implementation for Generating Comprehensive MetaFork Programs         | 158 |

| Cı | Curriculum Vitae 10 |                                                                       |     |

# **List of Figures**

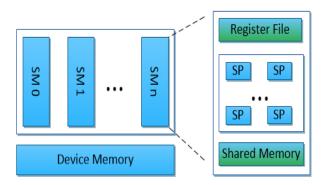

| 2.1  | GPU hardware architecture                                                       | (  |

|------|---------------------------------------------------------------------------------|----|

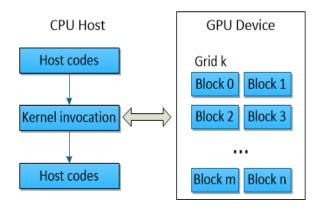

| 2.2  | Heterogeneous programming with GPU and CPU                                      | 7  |

| 3.1  | Example of a MetaFork program with a function spawn                             | 16 |

| 3.2  | Example of a MetaFork program with a parallel region                            | 17 |

| 3.3  | Example of a meta_for loop                                                      | 18 |

| 3.4  | Various variable attributes in a parallel region                                | 19 |

| 3.5  | Example of shared and private variables with meta_for                           | 19 |

| 3.6  | Parallel fib code using a function spawn                                        | 20 |

| 3.7  | Parallel fib code using a block spawn                                           | 20 |

| 3.8  | OpenMP clauses supported in the current program translations                    | 23 |

| 3.9  | A code snippet of an OpenMP sections example                                    | 25 |

| 3.10 | A code snippet showing how to exclude declarations which come from included     |    |

|      | header files                                                                    | 28 |

| 3.11 | A code snippet showing how to translate a parallel for loop from CilkPlus to    |    |

|      | MetaFork                                                                        | 28 |

|      | A code snippet showing how to insert a barrier from CilkPlus to MetaFork        | 28 |

| 3.13 | A code snippet showing how to handle data attribute of variables in the process |    |

|      | of outlining                                                                    | 32 |

| 3.14 | A code snippet showing how to translate parallel for loop from MetaFork to      | _  |

|      | CILKPLUS                                                                        | 32 |

|      | A general form of an OpenMP construct                                           | 32 |

|      | Translation of the OpenMP sections construct                                    | 34 |

|      | An array type variable                                                          | 36 |

|      | A code snippet translated from the codes in Figure 3.17                         | 36 |

|      | A scalar type variable                                                          | 36 |

|      | A code snippet translated from the codes in Figure 3.19                         | 36 |

|      | A code snippet showing the variable $m$ used as an accumulator                  | 36 |

|      | A MetaFork code snippet (right), translated from the left OpenMP codes          | 37 |

| 3.23 | A code snippet showing how to avoid adding redundant barriers when translat-    | _  |

|      | ing the codes from OpenMP to MetaFork                                           | 38 |

|      | Example of translation from MetaFork to OpenMP                                  | 39 |

|      | Example of translating a parallel function call from MetaFork to OpenMP         | 4( |

|      | Example of translating a parallel for loop from MetaFork to OpenMP              | 40 |

|      | A code snippet showing how to generate a new OpenMP main function               | 4( |

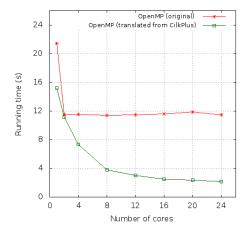

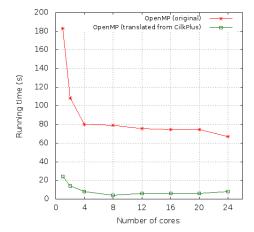

| 3.28 | Parallel mergesort in size 10 <sup>8</sup>                                      | 4  |

| 3.29 | Matrix inversion of order 4096                                                                                                                   | 43  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.30 | Matrix transpose : $n = 32768 \dots \dots$ | 44  |

| 3.31 | Naive Matrix Multiplication : $n = 4096$                                                                                                         | 44  |

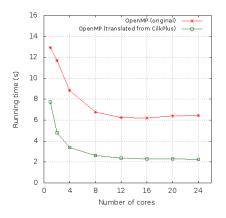

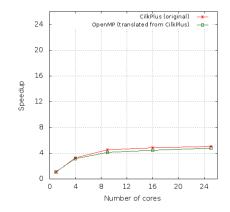

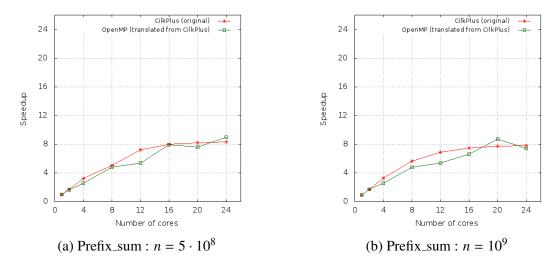

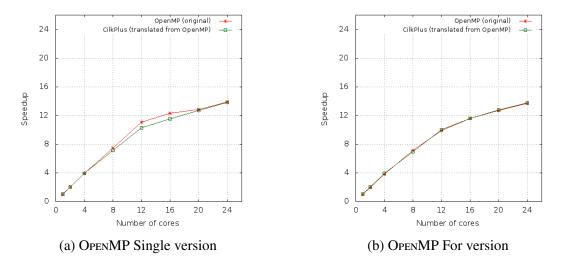

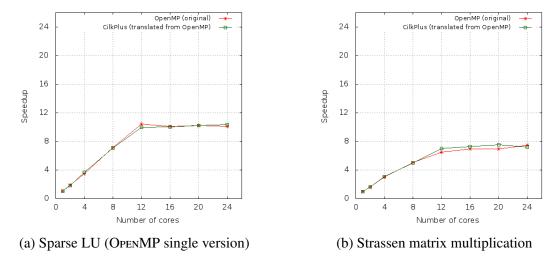

| 3.32 | Speedup curve on Intel node                                                                                                                      | 44  |

|      | Speedup curve on Intel node                                                                                                                      | 45  |

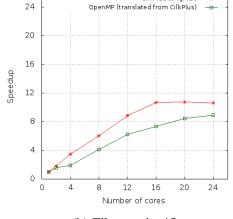

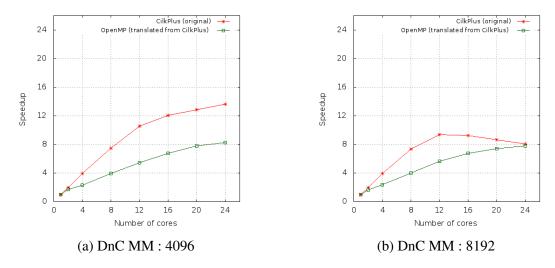

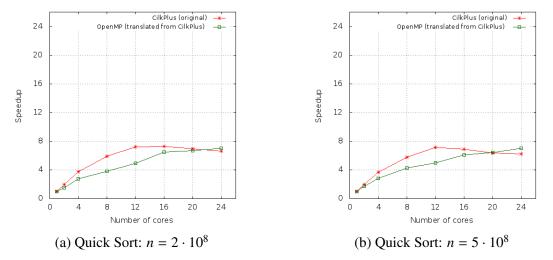

| 3.34 | Speedup curve on Intel node                                                                                                                      | 46  |

| 3.35 | Speedup curve on Intel node                                                                                                                      | 46  |

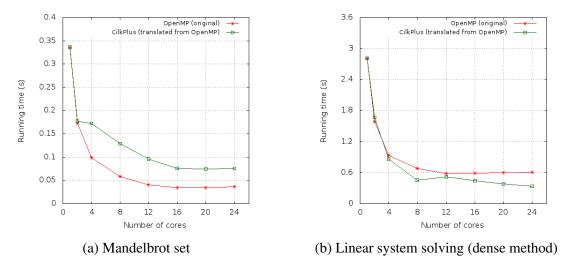

| 3.36 | Running time of Mandelbrot set and Linear system solving                                                                                         | 47  |

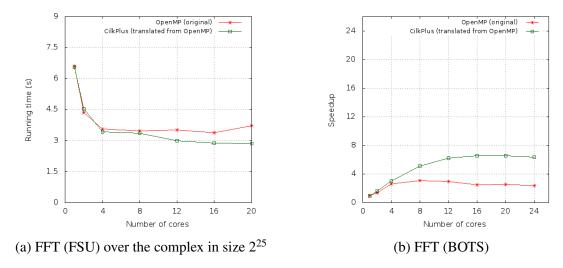

| 3.37 | FFT test-cases: FSU version and BOTS version                                                                                                     | 48  |

| 3.38 | Speedup curve of Protein alignment - 100 Proteins                                                                                                | 48  |

| 3.39 | Speedup curve of Sparse LU and Strassen matrix multiplication                                                                                    | 49  |

| 4.1  | MetaFork examples                                                                                                                                | 58  |

| 4.2  | Using meta_schedule to define one-dimensional CUDA grid and thread block                                                                         | 59  |

| 4.3  | Using meta_schedule to define two-dimensional CUDA grid and thread block                                                                         | 59  |

| 4.4  | Sequential C code computing Jacobi                                                                                                               | 60  |

| 4.5  | Generated MetaFork code from the code in Figure 4.4                                                                                              | 60  |

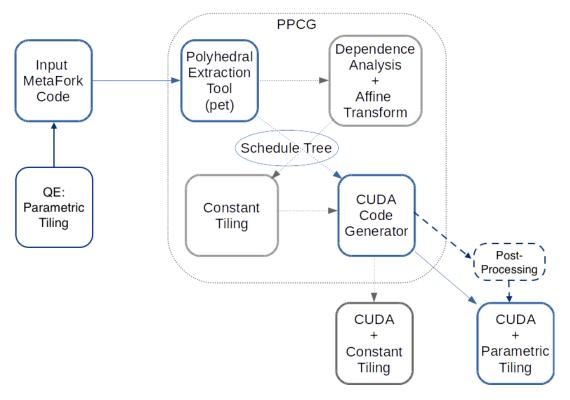

| 4.6  | Overview of the implementation of the MetaFork-to-CUDA code generator                                                                            | 61  |

| 4.7  | Generated parametric CUDA kernel for 1D Jacobi                                                                                                   | 62  |

| 4.8  | Generated host code for 1D Jacobi                                                                                                                | 63  |

| 4.9  | Serial code, MetaFork code and generated parametric CUDA kernel for array                                                                        |     |

|      | reversal                                                                                                                                         | 65  |

| 4.10 | Serial code, MetaFork code and generated parametric CUDA kernel for 2D                                                                           |     |

|      | Jacobi                                                                                                                                           | 67  |

| 4.11 | Serial code, MetaFork code and generated parametric CUDA kernel for LU                                                                           | ((  |

| 1 12 | decomposition                                                                                                                                    | 69  |

| 4.12 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix                                                                       | 70  |

| 1 12 | transpose                                                                                                                                        | /(  |

| 4.13 | addition                                                                                                                                         | 71  |

| 4.14 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix                                                                       | , - |

| .,   | vector multiplication                                                                                                                            | 71  |

| 4.15 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix                                                                       |     |

|      | matrix multiplication                                                                                                                            | 72  |

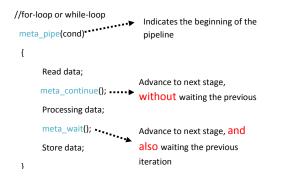

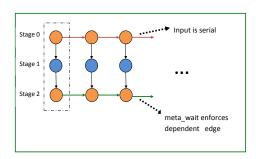

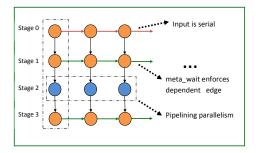

| 5.1  | Pipelining code with meta_pipe construct and its DAG                                                                                             | 76  |

| 5.2  | METAFORK pipelining code and its serial C-elision counterpart code                                                                               | 77  |

| 5.3  | Computation DAG of algorithms in Figure 5.2                                                                                                      |     |

| 5.4  | Stencil code using meta_pipe and its serial C-elision counterpart code                                                                           | 78  |

| 6.1  | MetaFork Pragma directive syntax                                                                                                                 | 81  |

| 6.2  | A code snippet showing a MetaFork program with Pragma directives                                                                                 | 82  |

| 6.3  | A code snippet showing a MetaFork program with keywords                                                                                          |     |

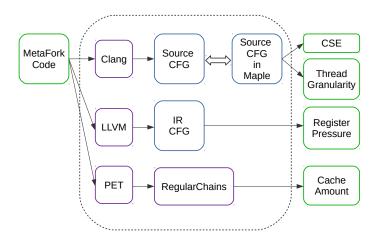

| 6.4  | Overall work-flow of the MetaFork compilation framework                                                                                          |     |

| 6.5  | A code snippet showing how to create tools based on CLANG's LibTooling                                                                           |     |

| 6.6         | A general command-line interface of MetaFork tools                             | 85             |

|-------------|--------------------------------------------------------------------------------|----------------|

| 6.7         | Overall work-flow of the MetaFork analysis and transformation chain            | 86             |

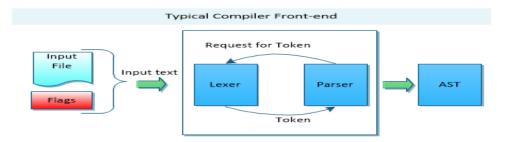

| 6.8         | Overall work-flow of the Clang front-end                                       | 88             |

| 6.9         | A code snippet showing how to create a MetaFork user defined PragmaHandler     | 88             |

| 6.10        | A code snippet showing how to register a new user defined Pragma handler       | 00             |

| C 11        | instance to Clang preprocessor                                                 | 89             |

|             | Convert MetaFork Keywords to Pragma directives                                 | 91             |

| 6.12        | A code snippet showing how to annotate a parallel for loop with MetaFork       | Ω1             |

| ( 12        | Pragma directive                                                               | 91             |

| 6.13        | A code snippet showing how to annotate a parallel for loop with MetaFork       | 0.1            |

| C 1 A       | keyword                                                                        | 91             |

|             | The code snippet after preprocessing the code in Figure 6.13                   | 92             |

|             | Setting the tok::eod token                                                     | 92             |

| 6.16        | A code snippet showing how to annotate a parallel region with MetaFork         | 00             |

| ( 17        | Pragma directive                                                               | 92             |

| 6.17        | A code snippet showing how to annotate a parallel region with MetaFork key-    | 93             |

| <i>(</i> 10 | word                                                                           |                |

|             | The code snippet after preprocessing the code of Figure 6.17                   | 93             |

|             | Consuming the shared clause                                                    | 93             |

| 6.20        | A code snippet showing how to annotate a join construct with MetaFork Pragma   | 02             |

| 6 21        | directive                                                                      | 93             |

| 0.21        | A code snippet showing how to annotate a join construct with MetaFork Keywords | 94             |

| 6 22        | The code snippet after preprocessing the code of Figure 6.21                   | 94             |

|             | A code snippet showing how to annotate device code with MetaFork Pragma        | 7 <del>1</del> |

| 0.23        | directive                                                                      | 94             |

| 6 24        | A code snippet showing how to annotate device code with MetaFork Keywords      | 95             |

|             | The code snippet after preprocessing the code of Figure 6.24                   | 95             |

|             | Convert CilkPlus Keywords to Pragma directives                                 | 95             |

|             | A code snippet showing how to annotate a parallel for loop with CILKPLUS       | ) )            |

| 0.27        | Pragma directive                                                               | 95             |

| 6.28        | A code snippet showing how to annotate a parallel for loop with CILKPLUS       | ,,             |

| 0.20        | keyword                                                                        | 95             |

| 6.29        | The code snippet after preprocessing the code Figure 6.28                      | 95             |

|             | A code snippet showing how to annotate a parallel function call with CILKPLUS  |                |

|             | Pragma directive                                                               | 96             |

| 6.31        | A code snippet showing how to annotate a parallel function call with CILKPLUS  |                |

|             | keyword                                                                        | 96             |

| 6.32        | The code snippet after preprocessing the code of Figure 6.31                   | 96             |

|             | A code snippet showing how to annotate a sync construct with CILKPLUS Pragma   |                |

|             | directive                                                                      | 96             |

| 6.34        | A code snippet showing how to annotate a sync construct with CILKPLUS Key-     |                |

|             | word                                                                           | 96             |

| 6.35        | The code snippet after preprocessing the code of Figure 6.34                   | 96             |

| 7.1  | Matrix addition written in C (the left-hand portion) and in MetaFork (the right-    |

|------|-------------------------------------------------------------------------------------|

|      | hand portion) with a meta_for loop nest, respectively                               |

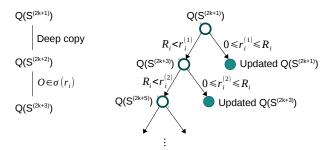

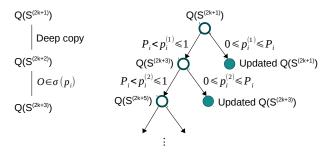

| 7.2  | Comprehensive translation of MetaFork code to two kernels for matrix addition 100   |

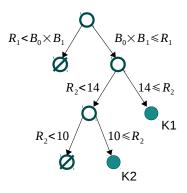

| 7.3  | The decision tree for comprehensive parametric CUDA kernels of matrix addition 101  |

| 7.4  | Matrix vector multiplication written in C (the left-hand portion) and in MetaFork   |

|      | (the right-hand portion), respectively                                              |

| 7.5  | The decision subtree for resource or performance counters                           |

| 7.6  | The serial elision of the MetaFork program for matrix vector multiplication 113     |

| 7.7  | The software tools involved for the implementation                                  |

| 7.8  | Computing the amount of words required per thread-block for reversing a 1D          |

|      | array                                                                               |

| 7.9  | The first case of the optimized MetaFork code for array reversal 117                |

| 7.10 | The second case of the optimized MetaFork code for array reversal 117               |

| 7.11 | The third case of the optimized MetaFork code for array reversal 117                |

| 7.12 | The first case of the optimized MetaFork code for matrix vector multiplication 118  |

| 7.13 | The second case of the optimized MetaFork code for matrix vector multiplication 118 |

| 7.14 | The third case of the optimized MetaFork code for matrix vector multiplication 119  |

| 7.15 | The MetaFork source code for 1D Jacobi                                              |

|      | The first case of the optimized MetaFork code for 1D Jacobi                         |

|      | The second case of the optimized MetaFork code for 1D Jacobi 120                    |

| 7.18 | The third case of the optimized MetaFork code for 1D Jacobi                         |

|      | The first case of the optimized MetaFork code for matrix addition 121               |

|      | The second case of the optimized MetaFork code for matrix addition 122              |

|      | The third case of the optimized MetaFork code for matrix addition 122               |

|      | The first case of the optimized MetaFork code for matrix transpose 122              |

|      | The second case of the optimized MetaFork code for matrix transpose 123             |

|      | The third case of the optimized MetaFork code for matrix transpose 123              |

|      | The first case of the optimized MetaFork code for matrix multiplication 124         |

|      | The second case of the optimized MetaFork code for matrix multiplication 124        |

| 7.27 | The third case of the optimized MetaFork code for matrix multiplication 125         |

| B.1  | PPCG code and generated CUDA kernel for array reversal                              |

| B.2  | PPCG code and generated CUDA kernel for matrix addition                             |

| B.3  | PPCG code and generated CUDA kernel for 1D Jacobi                                   |

| B.4  | PPCG code and generated CUDA kernel for 2D Jacobi                                   |

| B.5  | PPCG code and generated CUDA kernel for LU decomposition                            |

| B.6  | PPCG code and generated CUDA kernel for matrix vector multiplication 156            |

| B.7  | PPCG code and generated CUDA kernel for matrix transpose                            |

| B.8  | PPCG code and generated CUDA kernel for matrix multiplication 157                   |

# **List of Tables**

| 3.1 | OPENMP code                                                                                   | 50  |

|-----|-----------------------------------------------------------------------------------------------|-----|

|     | underlined timings to translated code                                                         | 50  |

| 4.1 | Speedup comparison of reversing a one-dimensional array between PPCG and MetaFork kernel code | 65  |

| 4.2 | Speedup comparison of 1D Jacobi between PPCG and MetaFork kernel code .                       | 65  |

| 4.3 | Speedup comparison of 2D Jacobi between PPCG and MetaFork kernel code .                       | 66  |

| 4.4 | Speedup comparison of LU decomposition between PPCG and MetaFork ker-                         |     |

|     | nel code                                                                                      | 68  |

| 4.5 | Speedup comparison of matrix transpose between PPCG and MetaFork kernel                       |     |

|     | code                                                                                          | 68  |

| 4.6 | Speedup comparison of matrix addition between PPCG and MetaFork kernel                        |     |

|     | code                                                                                          | 70  |

| 4.7 | Speedup comparison of matrix vector multiplication among PPCG kernel code,                    |     |

|     | MetaFork kernel code and MetaFork kernel code with post-processing                            | 70  |

| 4.8 | Speedup comparison of matrix multiplication between PPCG and MetaFork                         |     |

|     | kernel code                                                                                   | 72  |

| 4.9 | Timings (in sec.) of quantifier elimination for eight examples                                | 73  |

| 6.1 | MetaFork constructs and clauses                                                               | 90  |

| 6.2 | CILKPLUS constructs and clauses                                                               |     |

| 0.2 | CILKI LOS CONSTIUCIS ANA CIAUSCS                                                              | 93  |

| 7.1 | Optimization strategies with their codes                                                      | 116 |

# **List of Appendices**

| Appendix A Code Translation Examples                                         | . 14 | 1  |

|------------------------------------------------------------------------------|------|----|

| Appendix B Examples Generated by PPCG                                        | . 15 | ;3 |

| Appendix C The Implementation for Generating Comprehensive MetaFork Programs | . 15 | 58 |

# **Chapter 1**

# Introduction

In the past fifteen years, the pervasive ubiquity of multi-core processors has stimulated a constantly increasing effort in the development of concurrency platforms, such as CilkPlus [22, 98, 78], OpenMP [117, 14] and TBB [77]. While those programming languages are all based on the fork-join concurrency model [23], they largely differ in their way of expressing parallel algorithms and scheduling the corresponding tasks. Therefore, developing software code combining libraries written with several of those languages is a challenge.

Nevertheless there is a real need for facilitating interoperability between concurrency platforms. Consider for instance the field of symbolic computation. The DMPMC library <sup>1</sup> provides sparse polynomial arithmetic and is entirely written in OpenMP, meanwhile the BPAS library <sup>2</sup> provides dense polynomial arithmetic and is entirely written in CilkPlus. Polynomial system solvers require both sparse and dense polynomial arithmetic and thus could take advantage of a combination of the DMPMC and BPAS libraries. However, CilkPlus and OpenMP have different run-time systems. In order to achieve interoperability between them, an automatic source-to-source translation mechanism was desirable, yielding the original objective for this thesis work.

Another motivation for such a software tool is *comparative implementation* with the objective of narrowing performance bottlenecks. The underlying observation is that the same multi-threaded algorithm, based on the fork-join parallelism model, implemented with two different concurrency platforms, say CilkPlus and OpenMP, could result in very different performance, often very hard to analyze and compare. If one code scales well while the other does not, one may suspect an inefficient implementation of the latter as well as other possible causes such as higher level of parallelism overheads. Translating the inefficient code to the other language can help narrowing the problem. Indeed, if the translated code still does not scale, one can suspect an implementation issue (say the programmer missed to parallelize one critical portion of the algorithm) whereas if the translated code does scale, then one can suspect a parallelism overhead issue in the original code (say the grain-size of a parallel for-loop is too small).

In the past decade, the introduction of low-level heterogeneous programming models, in particular CUDA [5, 116], has brought super-computing to the level of the desktop com-

<sup>&</sup>lt;sup>1</sup>From the TRIP project www.imcce.fr/trip developed at the *Observatoire de Paris*

<sup>&</sup>lt;sup>2</sup> From the *Basic Polynomial Algebra Subprograms* www.bpaslib.org developed at the University of Western Ontario

puter. However, these models bring notable challenges, even to expert programmers. Indeed, fully exploiting the power of hardware accelerators, in particular Graphics Processing Units (GPUs) [106], with CUDA-like code often requires significant code optimization effort. While this development can indeed yield high performance [12], it is desirable for some programmers to avoid the explicit management of device initialization and data transfer between memory levels. To this end, high-level models for accelerator programming have become an important research direction. With these models, programmers only need to annotate their C/C++ code to indicate which code portion is to be executed on the device and how data maps between host and device.

As a consequence, it is desirable for our proposed source-to-source translation framework not to restrict itself to programming languages based on the fork-join concurrency model, but also to include the low-level heterogeneous programming model of CUDA which mainly relies on the *Single Instruction Multiple Data* (SIMD) paradigm, yielding the second motivation of this thesis work.

As of today, OpenMP and OpenACC [6, 144] are among the most developed accelerator programming models. Both OpenMP and OpenACC are built on a host-centric execution model. The execution of the program starts on the host and may offload target regions to the device for execution. The device may have a separated memory space or may share memory with the host, so that memory coherence is not guaranteed and must be handled by the programmer. In OpenMP and OpenACC, the division of the work between thread blocks within a grid and, between threads within a thread block can be expressed in a loose manner, or even ignored. This implies that code optimization techniques may be applied in order to derive efficient CUDA-like code. Of course, this is a non-obvious task for a variety of reasons. First of all, for portability reasons, the hardware characteristics of the targeted GPU device should not be assumed to be known in a source code written with a high-level models for accelerator programming. Secondly, and partially as a consequence, program parameters (like grid and thread block formats) should not be assumed to be known either in that same source code. Therefore, this source code should depend on parameters which are symbolic entities with unknown values at compile time.

Being able to generate (say from annotated C/C++) and optimize such parametric CUDA-like code is the third objective of this thesis work. As we shall see, achieving this objective leads to manipulate systems of non-linear polynomial constraints, which makes this process complex and challenging.

### 1.1 Dissertation Outline

In this thesis, we propose MetaFork which is both a language accommodating several models of concurrency (fork-join, pipelining, SIMD) and a compilation framework (performing automatic translation from CilkPlus to OpenMP, from OpenMP to CilkPlus, from annotated C/C++ to CUDA, etc.)

In Chapter 3, we present MetaFork as a metalanguage for multithreaded algorithms based on the fork-join parallelism model and targeting multi-core architectures. By its parallel programming constructs, the MetaFork language is currently a super-set of CilkPlus and offers

1.2. Contributions 3

counterparts for widely used parallel constructs of OpenMP. In Chapter 5, we show how the MetaFork language supports pipelining, allowing interoperability with Cilk-P [95].

The implementation of MetaFork as a compilation framework is presented mainly in Chapter 6. However, the software framework that allows automatic generation of CUDA code from annotated MetaFork programs is discussed in Chapter 4. Finally, Chapter 7 is dedicated to the question of optimizing parametric CUDA kernels and more generally, optimizing programs depending on parameters whose values are unknown at compile-time.

### 1.2 Contributions

METAFORK is a high-level programming language extending C/C++, which combines several models of concurrency including fork-join, SIMD and pipelining parallelism. MetaFork is also a compilation framework which aims at facilitating the design and implementation of concurrent programs through four key features which make MetaFork unique and novel:

- (1) Perform automatic code translation between concurrency platforms targeting multi-core architectures.

- (2) Provide a high-level language for expressing concurrency as in the fork-join model, the SIMD paradigm and the pipelining parallelism.

- (3) Generate parallel code from serial code with an emphasis on code depending on machine or program parameters (e.g. cache size, number of processors, number of threads per thread block).

- (4) Optimize code depending on parameters that are unknown at compile-time.

As of today, the publicly available and latest release of MetaFork, see www.metafork. org, offers the first three features stated above. The latter is implemented as a proof-of-concept and will be integrated in the public version in a near future.

### 1.3 Thesis Statement

Chapter 3 is a joint work with Marc Moreno Maza, Sushek Shekar and Priya Unnikrishnan, published as [35].

Chapter 4 is a joint work with Changbo Chen, Abdoul-Kader Keita, Marc Moreno Maza and Ning Xie, published as [29].

Chapters 5 and 6 are essentially my work under the supervision of Marc Moreno Maza and Abdoul-Kader Keita.

Chapter 7 is a joint work with Marc Moreno Maza and Ning Xie.

# Chapter 2

# **Background**

This chapter presents the technical background of our topic. Section 2.1 introduces the concurrency platforms that are relevant to better understand our work. Section 2.2 explains the most commonly used technologies and concepts to give insight into the performance of a parallel algorithm. Finally, a brief overview of directions for compiler research is covered in Section 2.3.

## 2.1 Concurrency Platforms

Nowadays, more and more promising parallel computing platforms are available for high performance computing. To gain speedup, programmers are expected to identify parallelism and choose suitable underlying platforms; otherwise, the algorithm developed might not display speedup, or even run slower than the sequential version. In the following sections, we summarize the basic properties of several concurrency platforms.

#### 2.1.1 CILKPLUS

CILKPLUS is a language extension to the C/C++ programming language, designed for task-based parallelism in a multithreaded environment. With the keywords introduced by CILKPLUS, a serial program can be easily converted into a parallel program which models a fork-join parallel control pattern that splits control flow into multiple parallel flows that re-join together later. Precisely, a CILKPLUS program is derived from a serial program annotated with CILKPLUS keywords indicating where parallelism is allowed. To boost applications, programmers only concentrate on developing the algorithm with ample parallelism, while leaving the underlying CILKPLUS run-time system with the responsibility of efficiently scheduling the computation on the executing processors. CILKPLUS uses a work stealing [24] strategy to schedule the computational tasks. This method can be efficiently implemented to map a large quantity of parallel tasks onto physical hardware resources at run-time. Moreover, the authors of [59] show that with its work stealing strategy, CILKPLUS programs are guaranteed to be time and space efficient. In particular, the computational tasks are adaptively load-balanced between worker threads in the CILKPLUS scheduler [99].

Note that CilkPlus keywords only denote the opportunity for parallel computation, but parallel computation is not mandatory. For example, the cilk\_spawn keyword which permits

the caller running in parallel with the callee, may not actually result in concurrency execution. To carry out such concurrency execution, there must be at least one thread that is idle and looks for computational tasks to steal from other threads. This implies that when a parallel CilkPlus program runs on a single core machine, the serial semantics of that program is retained.

To ease parallel programming efforts, there are two performance analysis tools, CILKPROF [72, 133] and CILKSCREEN [79], designed for programmers that use CILKPLUS. The CILKPROF scalability and performance analyzer is used to collect the parallel performance data of a CILKPLUS program. For example, CILKPROF profiles the work, span and burdened span, which allows the developers to diagnose performance bottlenecks in CILKPLUS programs. The CILKSCREEN race detector provides the programmers with any data races which are extremely hard to debug with serial programming tools.

#### **2.1.2** OPENMP

OPENMP (Open Multi-Processing) is the de-facto standard for programming multithreaded applications, which is primarily designed for shared memory systems before the release of version 4.0. By annotating a serial program with various OPENMP compiler directives, programmers can specify fork-join parallelism. Originally, OPENMP only supports implicit tasks for static parallelism which does not fit well into irregular applications which employ recursive algorithms, pointer chasing or load imbalances computation. To efficiently parallelize applications similarly to CilkPlus, OpenMP 3.0 extends its programming model, referred as the OpenMP tasking model [143], by allowing programmers to dynamically create asynchronous units of work to be scheduled by the run-time. The adoption of this tasking model broadens OpenMP to parallelize task-based applications as flexibly as CilkPlus.

Furthermore, beyond developing code for single address space parallelism, the OpenMP language committee has been working on a set of extensions to support heterogeneous computation model using both CPU and accelerators, and this work leads to the release of version 4.0 of the OpenMP specification in July, 2013. This accelerator model of OpenMP builds on a host-centric execution model. That is, the execution of an OpenMP program starts on the host (i.e. CPU) and the host may offload a piece of code to an attached accelerator device (e.g. GPU) for execution according to the OpenMP directives. The accelerator may have its separated memory space or may share memory space with the host, so that memory coherence [121] is not guaranteed.

The accelerator model in OpenMP is similar to OpenACC which also accelerates computation on an external accelerator by adding OpenACC compiler directives. OpenACC has been developed for several years, so the programming features of OpenACC are rich and stable. OpenMP, however, is just starting in the heterogeneous programming field, but it is catching up.

#### **2.1.3** GPU

In recent years, the use of GPUs as accelerators to offer more opportunities for performance tuning, has increased exponentially [52, 111, 45]. Contrary to the traditional CPU which is designed for serial processing, the GPU provides massive parallelism which is specialized for speeding up intensive computations. Programmers can take advantage of this programming

6 Chapter 2. Background

model to combine the power of CPU and GPU in order to explore massive parallelism. However, this model also introduces notable challenges [108], even for expert programmers, due to the complexity of GPU architectures, including memory hierarchy, thread hierarchy and hardware resource limitations. To exploit the computation capabilities efficiently, programmers are required to commit significant efforts in optimizing their algorithms with respect to specific hardware features [135, 84].

Figure 2.1: GPU hardware architecture

GPU Hardware Model. A GPU is made up of an array of streaming multiprocessors (SMs) that perform computations independently of each other, as well as off-chip device memory, as shown in Figure 2.1. As GPU architecture is evolving, the configuration and the number of SMs, and the amount of the device memory vary. Roughly, each SM consists of Scalar Processors (SPs), on-chip shared memory and register files. Register files and shared memory of each SM are statically and evenly allocated among thread blocks as long as they are active, and when context switching happens, the states of those registers and shared memory do not need to be saved and restored. This can be viewed as a key basis in achieving high throughput. A thread block which is composed of threads, is mapped to an SM and the execution of each thread block is completely independent of every other. Within a thread block, the SM splits the threads into warps of 32 threads which run in SIMD manner on SPs. In fact, from the perspective of GPUs, a warp is the basic scheduling and execution unit for an SM. Different warps within a thread block are scheduled asynchronously, but can be synchronized if needed. When one warp is stalled, the SM can quickly switch to other warps if they are ready, thereby effectively tolerating the long latency operations such as memory loads, and maximizing resource utilization.

GPU **Programming Model.** Programming GPUs for general-purpose applications is accomplished by the Compute Unified Device Architecture (CUDA) programming model. CUDA allows programmers to define functions, called kernels, which are executed with the SIMD mode by a large mount of threads on GPUs. Figure 2.2 illustrates the heterogeneous programming model of CUDA through a hybrid CPU/GPU computing approaches. That is, the execution of a CUDA program starts on the host (i.e. CPU) and the parallel kernel code is executed on the device (i.e. GPU) either synchronously or asynchronously with respect to the host. After the

Figure 2.2: Heterogeneous programming with GPU and CPU

completion of kernel calls, control is returned back to the CPU thread. In order to carry out the computations on the device, the programmer is responsible for organizing the data transfers between the host and device memory, transfers in both directions being handled by the host.

CUDA abstracts execution on the GPU in the form of thousands of concurrent threads which are organized into a two-level thread hierarchy composed of the grid as the top level and thread blocks as the bottom level. The size of the grid and the thread blocks can be configured in multiple dimensions (one, two, or three dimensions) by the special parameters provided at kernel launch time. Note that, the configurations are chosen manually by programmers without the guarantee that they are optimal. CUDA kernels written as a single function, are executed by all threads in the grid; hence, each thread needs to distinguish itself from others and to access unique data portions to operate on. To this end, threads are able to query CUDA built-in variables (e.g. blockId, gridDim and threadIdx) and combine them to compute a unique identifier.

In addition, to achieve high memory bandwidth [150], GPUs offer a region of memory, called shared memory, which is private to every SM and can be used to share data at thread block scope. Compared to the slow off-chip GPU device memory which can be accessed by all the threads, the on-chip shared memory provides a very fast memory access speed which is comparable to the speed of register access. From the perspective of programming, programmers need to explicitly declare variables with the CUDA \_\_shared\_\_ keyword to make variables resident in shared memory.

#### 2.2 Performance Measurement

Capturing analytically the parallelism overheads (e.g. scheduling costs) that a concurrency platform imposes on an executing program is a crucial question which has received little attention in the literature. However, establishing the leading cause of a performance issue often remains a very challenging task in many practical situations. Indeed, low parallelism or high cache-complexity at the algorithm level, ineffective implementation, hardware limitations and scheduling overheads are very different possible causes of poor performance. This section is devoted to discussing research directions to help with this challenge, targeting standard concurrency platforms on multi-core and many-core architectures.

#### 2.2.1 Occupancy and ILP

A key motivation [36] of GPUs for massive parallelism is to handle a large mount of active warps, i.e. groups of threads executing in SIMD fashion, on each SM. An SM maximizes utilization of its SIMD lanes [129] by multiplexing those warps according to their states. That is, when a warp which is running, stalls due to long memory or ALU operations latency, this warp is switched out and marked as pending, while another warp which is eligible will be switched in for execution. When the long latency operations complete, the pending warp that was switched out early becomes eligible for execution. Ideally, if there are sufficiently many warps at each cycle to tolerate latency, full computation resource utilization of the SM is achieved. Hence, utilization of an SM is directly associated with the number of active warps on that SM. The occupancy metric on GPUs is used to formulate this concept. Occupancy for an SM is defined as the ratio of the number of active warps to the maximum number of warps. A CUDA occupancy calculator tool, included in the CUDA toolkit, helps programmers to compute the occupancy for a kernel, depending on the execution configurations and the nature of the kernel algorithms.

In practice, to improve occupancy, programmers usually configure more thread blocks than SMs, as well as more threads than SPs. However, not all those thread blocks are concurrently active on SMs. To be active, the resources, such as register and shared memory usage, requested by a thread block, must be available. Thus, occupancy for each SM is tightly constrained by the limited amount of SM resources. As reported in [84, 88, 94], even a slight increase in resource usage, like per-thread register usage and per-block shared memory usage, could deliver a sharp occupancy degradation.

Empirically, occupancy poses a distinctive impact on performance according to the kernel computation patterns. For memory-intensive applications [51, 112, 145], larger occupancy is better due to the fact that instruction level parallelism (ILP) [149] within each thread is not sufficient to mask long memory access latency, and maximizing occupancy allows hiding the memory access latency by multiplexing the active warps. Nevertheless, optimizing for occupancy does not always equate to gain better performance. As revealed in [114, 149], in the context of computation-intensive applications, better performance can also be achieved at a relatively lower occupancy by exploiting more independent work per thread, i.e. ILP. Keep in mind that GPU threads do not stall on memory access and stall only when any operand is not ready. So under this circumstance, the memory access latency can be hidden at the overlapping execution of independent instructions. This idea is widely applied by code optimization. For example, loop unrolling [63, 114] creates a larger number of available independent instructions inside the loop body at the expense of increasing register pressure which may lead to the degradation of occupancy; however, the compiler has more opportunities in scheduling those instructions to improve ILP which maybe sufficient to offset the loss of thread-level parallelism. Hence, the balance between the number of active warps and the hardware resources available for a thread (or a thread block), is directly related to performance, and by choosing optimal kernel execution configurations as well as re-designing the kernel functions, the inter-convertibility between ILP and occupancy can be leveraged for performance tuning.

#### 2.2.2 Work-Span Model

In the work-span model, a program's execution can be seen as a directed acyclic graph (DAG) composed of nodes and edges. A DAG node represents a sequence of instructions without any parallel control instructions, and edges represent dependencies between nodes. The execution of a DAG follows the prescribed order, where a node of the DAG is eligible to run only if all its predecessor nodes have completed. In order to measure the parallelism using the work-span model, two fundamental metrics, work and span, are derived from DAGs. The work, denoted  $T_1$ , is the total time needed to execute the DAG serially. The span, denoted  $T_{\infty}$ , is also called the critical path length and is the execution time of the DAG on an ideal machine with an infinite number of processors.

In fact, the work-span model [23] has been used to support the development of the CilkPlus programming language and its implementation. Two complexity measures, the work  $T_1$  and the span  $T_{\infty}$  and one machine parameter, the number P of processors, are combined in results like the Graham-Brent theorem [23] or the Blumofe-Leiserson theorem (Theorems 13 & 14) [24] in order to compare algorithm running time estimates. We recall that the Graham-Brent theorem states that the running time  $T_P$  on P processors satisfies  $T_P \leq T_1/P + T_{\infty}$ .

When designing a parallel algorithm, it is desirable to systematically integrate the expected scheduling costs that a given concurrency platform imposes on this algorithm. To this end, a refinement of the fork-join model was proposed by He et al. [72] together with an enhanced version of the Graham-Brent theorem, which actually supports the implementation (on multicore architectures) of the parallel performance analyzer called Cilkview. In this context, the running time  $T_P$  is bounded in expectation by  $T_1/P + 2\Delta \widehat{T}_{\infty}$ , where  $\Delta$  is a constant (called the span coefficient) and  $\widehat{T}_{\infty}$  is the burdened span. Frigo et al. [59] describe the implementation of the CilkPlus work-stealing scheduler. They introduce the notions of work overhead and span overhead. Spoonhower et al. [139] present a theoretical concept of deviation on which we could rely in order to perform parallelism overhead analysis in the context of schedulers based on other principles than the randomized work-stealing. In particular, and as mentioned by Haque [70], analyzing the burden span may help us discover that an algorithm is not appropriate for an architecture.

#### 2.2.3 Master Theorem

The divide-and-conquer technique, as a classical approach for designing algorithms (either serial or parallel), is widely used [62, 15]. It applies in the case that a task with input size n, can be partitioned into smaller sub-tasks recursively, each with input size n/b, until a base-case problem is reached which is simple enough to be solved directly. Algorithms using this computational pattern can be parallelized efficiently with fork-join platforms, like CilkPlus and the tasking model in OpenMP, see [60].

The cost of divide-and-conquer algorithms illustrated above, can be represented as a recurrence relationship which is given by

$$T(n) = aT(n/b) + f(n)$$

(2.1)

where,

- 1. *n* is the input size of the original task.

- 2.  $a \ge 1$  and b > 1 are constants. a and n/b present the number of sub-tasks and the size of each sub-task, respectively.

- 3. f(n) is the cost of combining the answers of the sub-tasks.

- 4. T(n) is the cost of the task with input size n.

The complexity of the recurrence relationship in 2.1 can be easily solved by the master theorem [43] in the form of asymptotic notation. More precisely, T(n) is asymptotically bounded in three common cases as follows:

- 1. If  $f(n) = O(n^{\log_b a \epsilon})$  for some constant  $\epsilon > 0$ , then  $T(n) = \Theta(n^{\log_b a})$ .

- 2. If  $f(n) = \Theta(n^{\log_b a} \log^k n)$  for some  $k \ge 0$ , then  $T(n) = \Theta(n^{\log_b a} \log^{k+1} n)$ .