# Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

6-27-2011 12:00 AM

# Reliable and High-Performance Hardware Architectures for the Advanced Encryption Standard/Galois Counter Mode

Mehran Mozaffari-Kermani, The University of Western Ontario

Supervisor: Dr. Arash Reyhani-Masoleh, *The University of Western Ontario* A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering © Mehran Mozaffari-Kermani 2011

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Digital Circuits Commons, Hardware Systems Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Mozaffari-Kermani, Mehran, "Reliable and High-Performance Hardware Architectures for the Advanced Encryption Standard/Galois Counter Mode" (2011). *Electronic Thesis and Dissertation Repository*. 180. https://ir.lib.uwo.ca/etd/180

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

## RELIABLE AND HIGH-PERFORMANCE HARDWARE ARCHITECTURES FOR THE ADVANCED ENCRYPTION STANDARD/GALOIS COUNTER MODE

(Spine Title: Reliable and High-Performance Architectures for the AES/GCM) (Thesis Format: Monograph)

by

### Mehran <u>Mozaffari Kermani</u>

Graduate Program in Electrical and Computer Engineering

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada June 2011

© Mehran Mozaffari Kermani 2011

# THE UNIVERSITY OF WESTERN ONTARIO School of Graduate and Postdoctoral Studies

## CERTIFICATE OF EXAMINATION

Examination Board:

Dr. Amr M. Youssef

Supervisor:

Dr. Anestis Dounavis

Dr. Arash Reyhani-Masoleh

Dr. Hanan Lutfiyya

Dr. Xianbin Wang

The thesis by

#### Mehran <u>Mozaffari Kermani</u>

entitled:

#### Reliable and High-Performance Hardware Architectures for the Advanced Encryption Standard/Galois Counter Mode

is accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Chair of the Thesis Examination Board

Date

## Abstract

The high level of security and the fast hardware and software implementations of the Advanced Encryption Standard (AES) have made it the first choice for many critical applications. Since its acceptance as the adopted symmetric-key algorithm, the AES has been utilized in various security-constrained applications, many of which are power and resource constrained and require reliable and efficient hardware implementations.

In this thesis, first, we investigate the AES algorithm from the concurrent fault detection point of view. We note that in addition to the efficiency requirements of the AES, it must be reliable against transient and permanent internal faults or malicious faults aiming at revealing the secret key. This reliability analysis and proposing efficient and effective fault detection schemes are essential because fault attacks have become a serious concern in cryptographic applications. Therefore, we propose, design, and implement various novel concurrent fault detection schemes for different AES hardware architectures. These include different structure-dependent and independent approaches for detecting single and multiple stuck-at faults using single and multi-bit signatures.

The recently standardized authentication mode of the AES, i.e., Galois/Counter Mode (GCM), is also considered in this thesis. We propose efficient architectures for the AES-GCM algorithm. In this regard, we investigate the AES algorithm and we propose low-complexity and low-power hardware implementations for it, emphasizing on its nonlinear transformation, i.e., SubByes (S-boxes). We present new formulations for this transformation and through exhaustive hardware implementations, we show that the proposed architectures outperform their counterparts in terms of efficiency. Moreover, we present parallel, high-performance new schemes for the hardware implementations of the GCM to improve its throughput and reduce its latency.

The performance of the proposed efficient architectures for the AES-GCM and their fault detection approaches are benchmarked using application-specific integrated circuit (ASIC) and field-programmable gate array (FPGA) hardware platforms. Our comparison results show that the proposed hardware architectures outperform their existing counterparts in terms of efficiency and fault detection capability.

**Keywords:** Advanced Encryption Standard, finite field, Galois/Counter Mode, high performance, concurrent fault detection.

# Dedication

To my parents for their love, inspiration, and guidance.

# Acknowledgements

I would like to express my sincere appreciation and gratitude to Dr. Arash Reyhani-Masoleh for supervising my research during my Ph.D. studies. I would like to also thank my lab-mates, Dr. Arash Hariri, Christopher Kennedy, and Reza Azarderakhsh for sharing their experience and knowledge with me.

# Contents

| C        | ertifi | cate of Examination                                     | ii            |

|----------|--------|---------------------------------------------------------|---------------|

| A        | bstra  | $\operatorname{ct}$                                     | iii           |

| D        | edica  | tion                                                    | $\mathbf{iv}$ |

| A        | cknov  | wledgements                                             | $\mathbf{v}$  |

| Li       | st of  | Figures                                                 | ix            |

| Li       | st of  | Tables                                                  | xi            |

| Li       | st of  | Abbreviations                                           | xiii          |

| 1        | Intr   | oduction and Preliminaries                              | 1             |

|          | 1.1    | Advanced Encryption Standard                            | 2             |

|          |        | 1.1.1 LUT-Based Architectures                           | 3             |

|          |        | 1.1.2 Composite Field Architectures                     | 4             |

|          | 1.2    | The Galois/Counter Mode                                 | 4             |

|          | 1.3    | Motivation                                              | 7             |

|          | 1.4    | Thesis Outline                                          | 8             |

| <b>2</b> | Lite   | rature Review                                           | 9             |

|          | 2.1    | Fault Detection Schemes                                 | 9             |

|          | 2.2    | AES-GCM Architectures                                   | 13            |

| 3        | Per    | formance Evaluations and Comparisons of the AES S-boxes | 16            |

|          | 3.1    | Logic-gate Optimizations                                | 17            |

|          | 3.2    | Area and Delay Evaluations                              | 23            |

|          | 3.3                                                              | Power                                                     | Consumptions and Comparisons                                        | 25        |  |  |  |  |  |

|----------|------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------|-----------|--|--|--|--|--|

|          |                                                                  | 3.3.1                                                     | Power Derivation Method                                             | 25        |  |  |  |  |  |

|          |                                                                  | 3.3.2                                                     | Analysis and Comparison                                             | 25        |  |  |  |  |  |

| 4        | A L                                                              | ightwe                                                    | ight Fault Detection Scheme for the (Inverse) S-box Using           |           |  |  |  |  |  |

|          | Cor                                                              | nposite                                                   | e Fields                                                            | <b>28</b> |  |  |  |  |  |

|          | 4.1                                                              | Some 2                                                    | Notes on Polynomial and Normal Bases                                | 29        |  |  |  |  |  |

|          | 4.2                                                              | Fault 1                                                   | Detection Scheme                                                    | 31        |  |  |  |  |  |

|          |                                                                  | 4.2.1                                                     | The S-box and the Inverse S-box Using Polynomial Basis              | 31        |  |  |  |  |  |

|          |                                                                  | 4.2.2                                                     | The S-box and the Inverse S-box Using Normal Basis $\hdots$         | 34        |  |  |  |  |  |

|          | 4.3                                                              | Error                                                     | Simulations                                                         | 40        |  |  |  |  |  |

|          | 4.4                                                              | ASIC                                                      | and FPGA Implementations and Comparisons                            | 41        |  |  |  |  |  |

| <b>5</b> | A I                                                              | igh-Po                                                    | erformance Concurrent Fault Detection Approach for the              |           |  |  |  |  |  |

|          | Cor                                                              | Composite Field (Inverse) S-box                           |                                                                     |           |  |  |  |  |  |

|          | 5.1                                                              | 1 S-box and Inverse S-box Arithmetic Used in This Chapter |                                                                     |           |  |  |  |  |  |

|          | 5.2                                                              | 2 Proposed Fault Detection Approach                       |                                                                     |           |  |  |  |  |  |

|          |                                                                  | 5.2.1                                                     | S-box                                                               | 49        |  |  |  |  |  |

|          |                                                                  | 5.2.2                                                     | Inverse S-box                                                       | 52        |  |  |  |  |  |

|          |                                                                  | 5.2.3                                                     | Merged S-box and Inverse S-box                                      | 55        |  |  |  |  |  |

|          |                                                                  | 5.2.4                                                     | Complexity Analysis                                                 | 55        |  |  |  |  |  |

|          | 5.3                                                              | 3 Simulation Results                                      |                                                                     |           |  |  |  |  |  |

|          | 5.4                                                              | 4 ASIC Implementations and Comparisons                    |                                                                     |           |  |  |  |  |  |

|          | 5.5                                                              | Formu                                                     | lations for Mixed Bases                                             | 69        |  |  |  |  |  |

|          |                                                                  | 5.5.1                                                     | Other Variants                                                      | 73        |  |  |  |  |  |

| 6        | Concurrent Structure-Independent Fault Detection Schemes for the |                                                           |                                                                     |           |  |  |  |  |  |

|          | AE                                                               | S                                                         |                                                                     | 74        |  |  |  |  |  |

|          | 6.1                                                              | Notati                                                    | ons Used in This Chapter                                            | 75        |  |  |  |  |  |

|          |                                                                  | 6.1.1                                                     | AES Encryption                                                      | 76        |  |  |  |  |  |

|          |                                                                  | 6.1.2                                                     | AES Decryption                                                      | 77        |  |  |  |  |  |

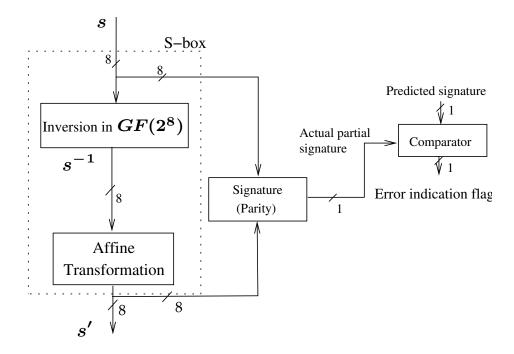

|          | 6.2                                                              | A New                                                     | Fault Detection Scheme for the S-box and the Inverse S-box $\ldots$ | 78        |  |  |  |  |  |

|          |                                                                  | 6.2.1                                                     | The Systematic Scheme for the Multiplicative Inversion              | 78        |  |  |  |  |  |

|    |        | 6.2.2   | The Proposed Scheme for the S-box and the Inverse S-box $\ . \ . \ .$ | 81  |

|----|--------|---------|-----------------------------------------------------------------------|-----|

|    | 6.3    | Propo   | sed Fault Detection Schemes for the AES                               | 85  |

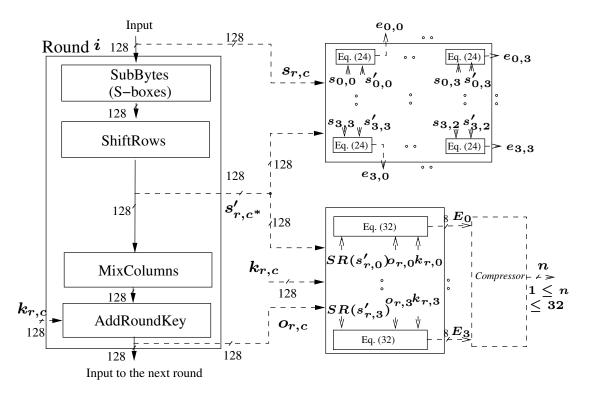

|    |        | 6.3.1   | AES Encryption                                                        | 86  |

|    |        |         | SubBytes and ShiftRows                                                | 86  |

|    |        |         | MixColumns and AddRoundKey                                            | 87  |

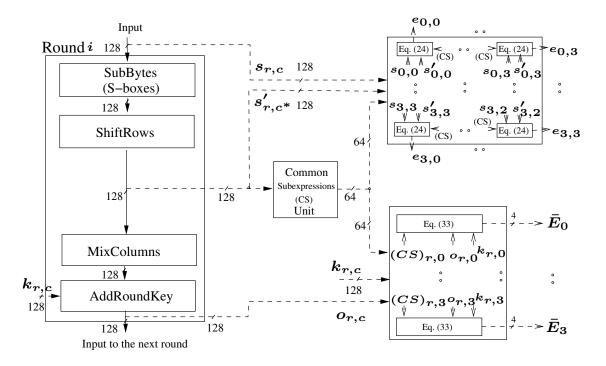

|    |        |         | Further Improvements                                                  | 89  |

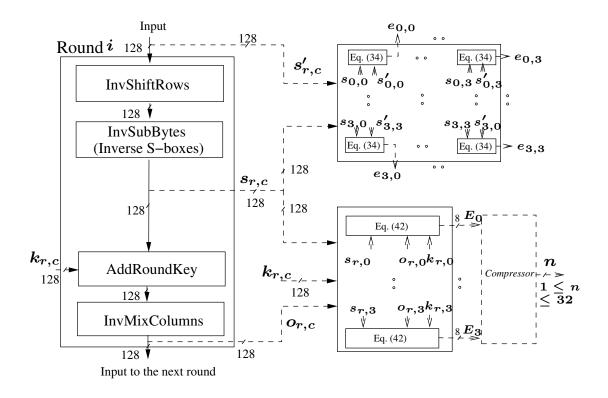

|    |        | 6.3.2   | AES Decryption                                                        | 91  |

|    |        |         | InvShiftRows and InvSubBytes                                          | 92  |

|    |        |         | AddRoundKey and InvMixColumns                                         | 92  |

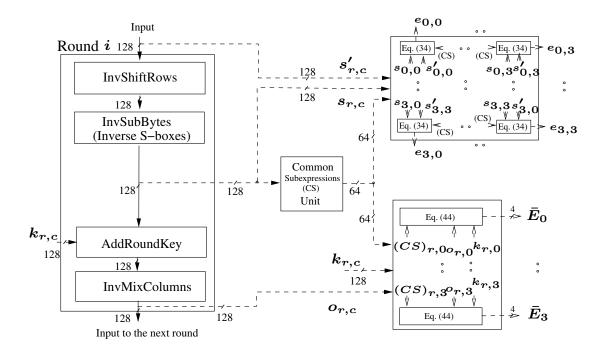

|    |        |         | Further Improvements                                                  | 95  |

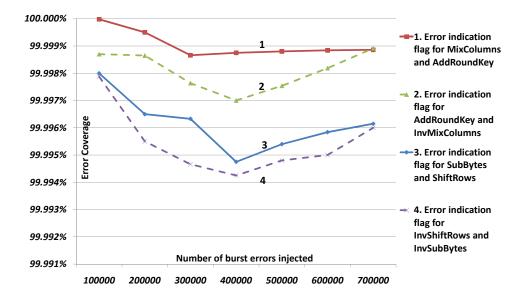

|    | 6.4    | Error   | Simulations                                                           | 97  |

|    | 6.5    | AES I   | FPGA Implementations and Comparisons                                  | 99  |

| 7  | Effi   | cient a | and High-Performance Parallel Hardware Architectures for              |     |

| •  |        | AES-0   |                                                                       | 107 |

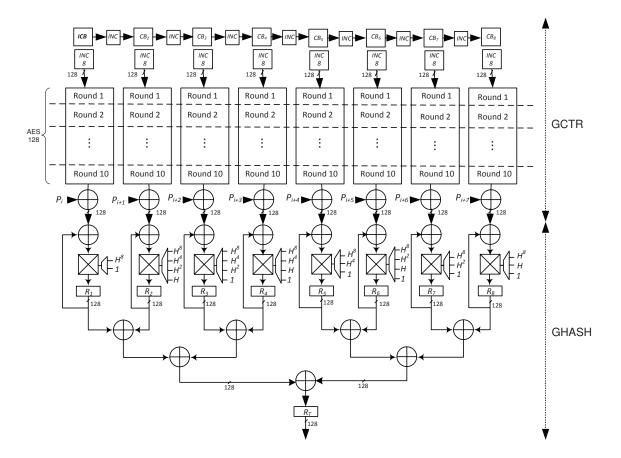

|    | 7.1    |         | Performance GCM Parallel Architecture                                 | 107 |

|    | (.1    |         |                                                                       |     |

|    |        | 7.1.1   | High-Performance $GHASH_H$ Function                                   | 108 |

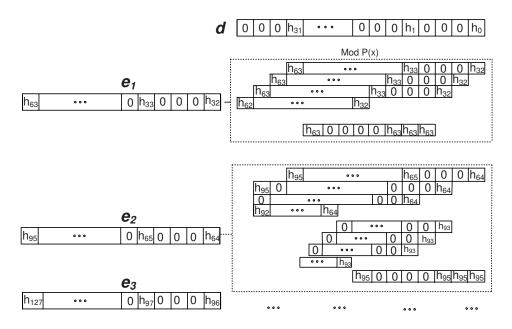

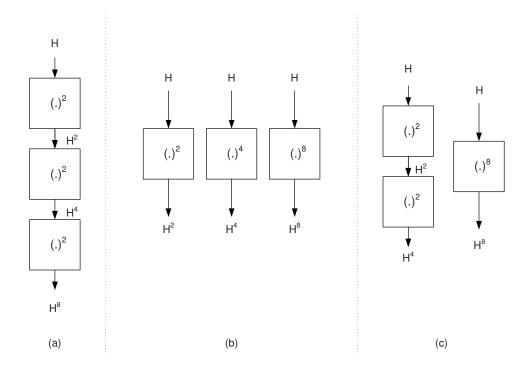

|    |        | 7.1.2   | High-Speed Structures for Hash Subkey Powers                          | 112 |

|    |        | 7.1.3   | $GF(2^{128})$ Multipliers for the GCM                                 | 115 |

|    | 7.2    | AES-0   | GCM Performance Comparisons                                           | 116 |

| 8  | Sun    | nmary   | and Future Work                                                       | 123 |

|    | 8.1    | Thesis  | Summary                                                               | 123 |

|    | 8.2    | Future  | e Work                                                                | 125 |

| P  |        |         |                                                                       |     |

| ום | ibliog | graphy  |                                                                       | 127 |

# List of Figures

| 1.1 | The AES encryption round transformations [1]                                                          | 3  |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 1.2 | The composite field S-box architecture using polynomial basis [20] and                                |    |

|     | normal basis [23]                                                                                     | 5  |

| 1.3 | The GCM authenticated encryption data flow [5]. $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 6  |

| 2.1 | Redundant unit fault detection structure for S-box (inverse S-box) [34], [42].                        | 10 |

| 2.2 | Parity-based fault detection structure of the $i_{th}$ round in the AES-128                           |    |

|     | encryption.                                                                                           | 11 |

| 2.3 | The multiplication-based scheme for the fault detection of the multiplica-                            |    |

|     | tive inversion $[38]$                                                                                 | 12 |

| 2.4 | Low-power S-box (resp. inverse S-box) architecture using composite fields                             |    |

|     | and polynomial basis [13].                                                                            | 13 |

| 2.5 | The sequential method used in [64], [65], and [66] for the hardware imple-                            |    |

|     | mentation of the $GHASH_H$                                                                            | 14 |

| 4.1 | The S-box (the inverse S-box) using composite fields and polynomial basis                             |    |

|     | [20] and their fault detection blocks. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 30 |

| 4.2 | The S-box (the inverse S-box) using composite fields and normal basis [23]                            |    |

|     | and their fault detection blocks                                                                      | 31 |

| 5.1 | The architecture of the S-box (resp. the inverse S-box) using composite                               |    |

|     | field and polynomial basis [20].                                                                      | 48 |

| 5.2 | The proposed parity-based fault detection scheme for the S-box (resp.                                 |    |

|     | inverse S-box).                                                                                       | 50 |

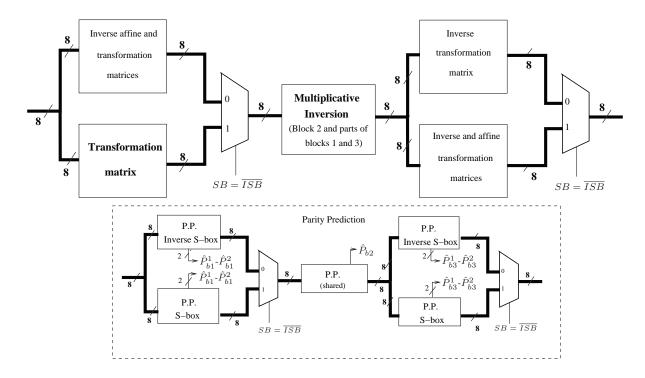

| 5.3 | Merged S-box (SB) and inverse S-box (ISB) and the corresponding pre-                                  |    |

|     | dicted parities for different blocks                                                                  | 56 |

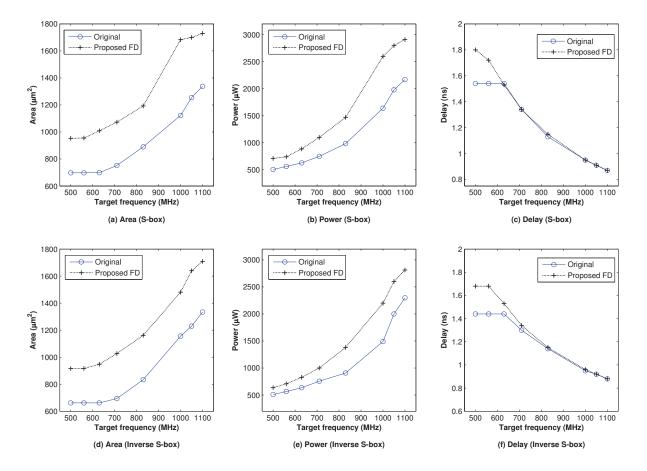

| 5.4 | The areas, critical path delays, and power consumptions of the original                                                     |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|

|     | [22] and the proposed fault detection S-box and inverse S-box                                                               | 67  |

| 5.5 | The Area, delay, and power consumption overheads of the proposed schemes                                                    |     |

|     | for the S-box and the inverse S-box                                                                                         | 68  |

| 5.6 | The presented fault detection structure for the mixed bases S-box [62]. $% \left[ \left( 1-\frac{1}{2}\right) \right) =0$ . | 70  |

| 6.1 | The proposed structure-independent fault detection scheme of the S-box.                                                     | 83  |

| 6.2 | The proposed fault detection scheme for the $ith$ round of the AES encryption.                                              | 87  |

| 6.3 | The proposed low-complexity fault detection scheme for the $ith$ round of                                                   |     |

|     | the AES encryption utilizing subexpression sharing                                                                          | 91  |

| 6.4 | The proposed fault detection scheme for the $ith$ round of the AES decryption.                                              | 93  |

| 6.5 | The proposed low-complexity fault detection scheme for the $ith$ round of                                                   |     |

|     | the AES decryption utilizing subexpression sharing                                                                          | 96  |

| 6.6 | Simulation results for the error coverages of the proposed fault detection                                                  |     |

|     | schemes                                                                                                                     | 99  |

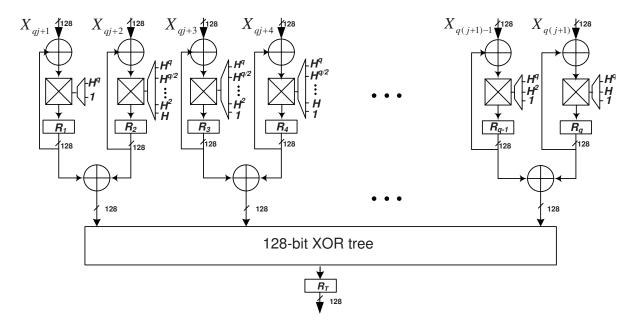

| 7.1 | The hardware architecture of the proposed high-performance GCM $GHASH_H$                                                    |     |

|     | function.                                                                                                                   | 110 |

| 7.2 | The derivation of $H^4$ of the GCM hash subkey                                                                              | 113 |

| 7.3 | (a) Cascade, (b) parallel, and (c) hybrid realization methods for the hash                                                  |     |

|     | subkey exponentiations.                                                                                                     | 114 |

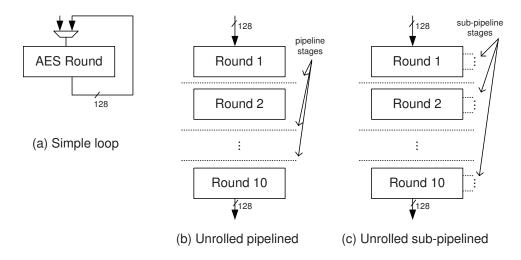

| 7.4 | The AES-128 structure for (a) simple loop, (b) unrolled pipelined, and (c)                                                  |     |

|     | unrolled sub-pipelined architectures (MixColumns is bypassed in the last                                                    |     |

|     | round)                                                                                                                      | 117 |

| 7.5 | The proposed AES-GCM high-performance architecture for $q = 8. \ldots 1$                                                    | 118 |

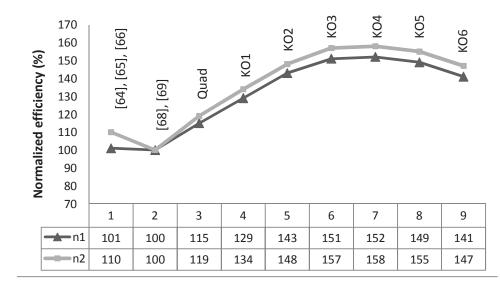

| 7.6 | Comparison of the efficiencies of nine different AES-GCM architectures                                                      |     |

|     | for $n_1 = 2^{32} - 2$ and $n_2 = 2^{10}$ .                                                                                 | 121 |

# List of Tables

| 3.1 | Evaluation of the performance metrics of the S-boxes on ASIC using the STM 65-nm CMOS standard technology.                                                    | 22 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Evaluation of the power consumptions of the S-boxes on ASIC using the STM 65-nm CMOS standard technology and the Synopsys <sup>®</sup> PrimeTime <sup>®</sup> |    |

|     | PX [73]                                                                                                                                                       | 27 |

| 4.1 | Area/delay complexities of blocks 1 and 5 of the S-box and their predicted parities for possible values of $\nu$ 's and $\Phi$ 's.                            | 35 |

| 4.2 | Parity predictions and complexities of block 2 of the normal basis S-box<br>for possible values of $\nu'$ and $\Phi'$ .                                       | 37 |

| 4.3 | Error simulation results of the optimum S-box and inverse S-box after injecting 500,000 errors.                                                               | 40 |

| 4.4 | ASIC implementations of the fault detection schemes for the S-box (SB)<br>and the inverse S-box using $0.18\mu$ CMOS technology.                              | 42 |

| 4.5 | Xilinx <sup>®</sup> Virtex <sup>TM</sup> -II Pro FPGA implementations (xc2vp2-7) of the fault detection schemes for the S-box (SB) and the inverse S-box.     | 43 |

| 4.6 | ASIC implementations of the fault detection schemes of the AES encryption using $0.18\mu$ CMOS technology.                                                    | 44 |

| 4.7 | Xilinx <sup>®</sup> Virtex <sup>TM</sup> -II Pro FPGA implementations of the fault detection<br>schemes of the AES encryption.                                | 44 |

| 5.1 | The timing details of the proposed concurrent scheme for the S-box and the inverse S-box.                                                                     | 57 |

| 5.2 | Fault detection capabilities of the proposed schemes after injecting 1,000,000         random multiple faults.                                                | 60 |

| 5.3 | Comparing the areas, critical path delays, power consumptions, and fault    |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | detection capabilities of the proposed and previously presented fault de-   |     |

|     | tection schemes for the S-box using the 65-nm CMOS standard technology.     | 62  |

| 5.4 | Comparing the areas, critical path delays, power consumptions, and fault    |     |

|     | detection capabilities of the proposed and previously presented fault de-   |     |

|     | tection schemes for the inverse S-box using the 65-nm CMOS standard         |     |

|     | technology                                                                  | 65  |

| 6.1 | Comparisons of the implementations of the fault detection schemes of the    |     |

|     | AES using LUT S-boxes and inverse S-boxes on Xilinx <sup>®</sup> FPGAs      | 101 |

| 6.2 | Implementation comparisons of the fault detection schemes of the AES        |     |

|     | encryption using composite field S-boxes on Xilinx <sup>®</sup> FPGAs       | 104 |

| 7.1 | Performance analysis and comparison of $GHASH_H$ within the GCM for $n$     |     |

|     | blocks and $q$ parallel structures                                          | 111 |

| 7.2 | Complexities of the realizations of the hash subkey exponentiations for     |     |

|     | $q = 8$ parallel architectures for $GHASH_H$                                | 115 |

| 7.3 | Hardware and timing complexities analysis of the utilized bit-parallel mul- |     |

|     | tipliers for the GCM                                                        | 116 |

| 7.4 | The proposed architecture for the AES-GCM                                   | 117 |

| 7.5 | ASIC synthesis comparisons of the AES-GCM using the STM 65-nm CMOS $$       |     |

|     | technology                                                                  | 120 |

# List of Abbreviations

| 3DES | Triple Data Encryption Standard                         |

|------|---------------------------------------------------------|

| AES  | Advanced Encryption Standard                            |

| ASIC | Application-Specific Integrated Circuit                 |

| DES  | Data Encryption Standard                                |

| FPGA | Field-Programmable Gate Array                           |

| GCM  | Galois/Counter Mode                                     |

| GF   | Galois Field                                            |

| LUT  | Look-up Table                                           |

| NIST | National Institute of Standards and Technology          |

| VHDL | Very-high-speed integrated circuit Hardware Description |

|      | Language                                                |

| VLSI | Very Large Scale Integration                            |

# Chapter 1 Introduction and Preliminaries

N this chapter, we present an introduction for this thesis. We also provide the preliminaries, motivations, and thesis outline.

Symmetric key cryptography uses a shared key in both sender and receiver ends during encryption and decryption for secure communications. For the drawbacks of the previous symmetric-key cryptographic standards such as the DES and the 3DES, they have been replaced by the Advanced Encryption Standard (AES) [1]. In particular, the AES has overcome the drawbacks of the previous standards in terms of vulnerability to brute force attacks and slow software implementations. The AES was accepted by the National Institute of Standards and Technology (NIST) in 2001 and since its acceptance, it has been utilized in a variety of security-constrained applications. For instance, it has been included in wireless standards of Wi-Fi [2] and WiMAX [3] and many other applications, ranging from the security of smart cards to the bitstream security mechanisms in FPGAs [4].

The Advanced Encryption Standard-Galois/Counter Mode (AES-GCM) provides authentication and confidentiality for sensitive data simultaneously. In the AES-GCM, data confidentiality is provided by the AES [1]. The authentication of the AES-GCM is provided by the Galois/Counter Mode (GCM) [5] using a universal hash function. The AES-GCM has been used for a number of applications such as the new LAN security standard WLAN 802.1ae (MACSec) [6] and Fibre Channel Security Protocols (FC-SP) [7]. Moreover, it has been utilized in a number of cores from industry, see, for example, [8], [9], and [10]. In addition, two AES-GCM software-based implementations have been presented in [11] and [12].

In what follows, we present the details on the AES and the GCM algorithms.

## **1.1** Advanced Encryption Standard

In the AES encryption, the input and the output blocks are limited to 128 bits. However, based on the security requirements, the key size could be determined as 128 (AES-128), 192 (AES-192) or 256 (AES-256). For each of these three types of the AES, different number of rounds corresponding to different levels of security objectives is utilized, i.e., for the AES-128, 10 rounds, for the AES-192, 12 rounds and for the AES-256, 14 rounds are processed [1]. In the AES encryption, four transformations in all the rounds, except for the last round which has three transformations, are utilized.

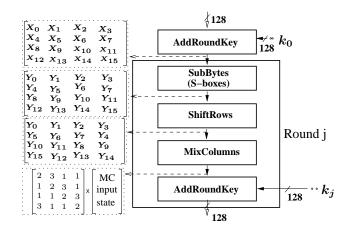

The AES encryption transformations for the typical round j are depicted in Fig. 1.1. The 128 bits of the input and output of each transformation are considered as four by four matrices, called *states* (shown in dotted rectangles in Fig. 1.1), whose entries are eight bits. The first transformation in each round is *SubBytes* (S-boxes), which is implemented by 16 S-boxes. In the S-box, each byte of the input state ( $X_i$ ,  $0 \le i \le 15$ , in Fig. 1.1) is substituted by a new byte ( $Y_i$ ,  $0 \le i \le 15$ , in Fig. 1.1). *ShiftRows* is the second transformation in which the first row of the state remains intact and the four bytes of the last three rows of the input state are cyclically shifted. The third transformation is *MixColumns* in which each column is modified individually. As shown in Fig. 1.1, the columns are considered as polynomials over  $GF(2^8)$  and are multiplied by a fixed polynomial. The final transformation is *AddRoundKey* which performs the modulo-2 addition of the input state and the key of the corresponding round, i.e.,  $k_j$ ,  $1 \le j \le 10$ , 12 or 14 for the AES-128, 192 or 256, respectively [1]. In the AES decryption, the reverse procedure of the AES encryption is performed [1].

For realizing the S-box, the irreducible polynomial of  $P(x) = x^8 + x^4 + x^3 + x + 1$ is used to construct the binary field  $GF(2^8)$ . Let  $X_i \in GF(2^8)$  and  $Y_i \in GF(2^8)$  be the input and the output of the S-box. Then, the S-box consists of finding the multiplicative inversion, i.e.,  $X_i^{-1} \in GF(2^8)$  with the exception of mapping the zero input to the zero output, followed by the affine transformation in  $GF(2^8)$  [1]. For the inverse S-boxes of the AES decryption, inverse affine transformation precedes the multiplicative inversion [1].

Among the four different transformations in the AES, only the S-box and the inverse S-box are non-linear. Additionally, all the S-boxes (resp. the inverse S-boxes) occupy

Figure 1.1: The AES encryption round transformations [1].

much of the total AES encryption (resp. decryption) area and their power consumption is around three fourths of that of the entire AES [13]. In what follows, we present the preliminaries regarding the hardware implementations of the S-boxes and the inverse S-boxes within the AES using look-up tables (LUTs) and composite fields.

#### 1.1.1 LUT-Based Architectures

The AES S-boxes and inverse S-boxes can be implemented using LUTs. For this purpose,  $256 \times 8$  memory cells are used to store the 256 possible 8-bit outputs of each S-box/inverse S-box. The LUT-based implementation is suitable for the field-programmable gate array (FPGA) platforms in which block memories are available, see, for example, [14], [15], and [16]. However, although this implementation reaches high-speed architectures, it is not suitable for applications requiring low-complexity AES application-specific integrated circuit (ASIC) implementations [17].

The S-box and the inverse S-box are nonlinear operations which take 8-bit inputs and generate 8-bit outputs. In the S-box, the irreducible polynomial of  $P(x) = x^8 + x^4 + x^3 + x + 1$  is used to construct the binary field  $GF(2^8)$ . The usage of arithmetic in composite fields reduces the space complexity of the S-box. Moreover, it allows us to use pipelining and therefore the effective speed of the AES is increased while processing independent messages. Consequently, the S-boxes and inverse S-boxes implemented using composite fields can lead to area-efficient and high-performance structures [17]. In the following, the preliminaries on composite field realizations are presented.

#### **1.1.2** Composite Field Architectures

In this section, we describe the composite field arithmetics to calculate the multiplicative inversion over  $GF(2^8)$ . This approach has received much attention in the literature, see, for example, [13], [17], [18], [19], [20], [21], [22], [23], [24], and [25]. Moreover, there have been low-power implementations for the S-boxes (resp. the inverse S-boxes) such as the ones in [13] and [26]. It is noted that the low-power S-box (resp. inverse S-box) presented in [13] uses composite fields.

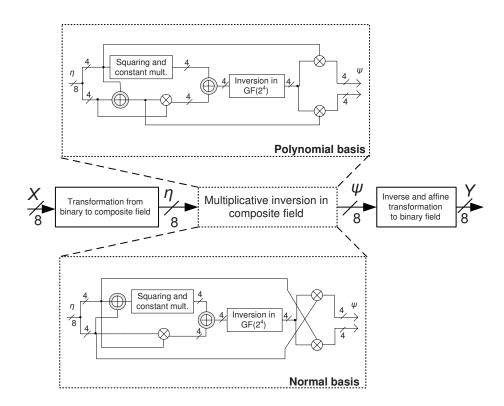

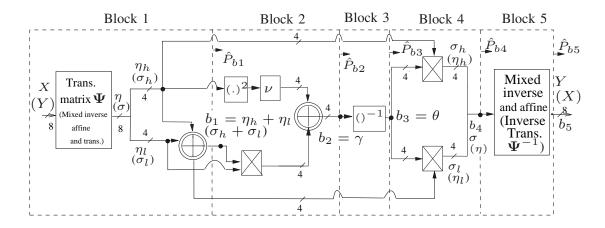

The composite fields can be represented using normal basis [23] or polynomial basis [18], [20], [21], [22]. The composite field realizations of the S-box using polynomial and normal bases are presented in Fig. 1.2. As seen in this figure, a transformation matrix transforms a field element  $X \in GF(2^8)$  to the corresponding representation in the composite field  $GF(16^2)$ , i.e.,  $\eta$ . We consider the irreducible polynomial of  $u^2 +$  $u + \nu$ , where  $\nu$  is chosen over GF(16) depending on the composite fields. Then, the multiplicative inversion generates the inverse as  $\psi = \eta^{-1}$ . Finally, as seen in Fig. 1.2, the inverse transformation matrix transforms the composite field element to the one in the binary field, i.e.,  $Y \in GF(2^8)$ .

Using polynomial basis constructed by the irreducible polynomial of  $u^2 + u + \nu$ , one can obtain the coordinates of  $\psi$  as  $\psi_h = \eta_h (\eta_h^2 \nu + \eta_h \eta_l + \eta_l^2)^{-1}$  and  $\psi_l = (\eta_l + \eta_h)(\eta_h^2 \nu + \eta_h \eta_l + \eta_l^2)^{-1}$  [20]. This multiplicative inversion in composite fields using polynomial basis is shown in the top part of Fig. 1.2 by a dotted rectangle. Similarly, for normal basis, the coordinates of  $\psi$  are obtained as  $\psi_h = (\eta_h \eta_l + (\eta_h^2 + \eta_l^2)\nu)^{-1}\eta_l$  and  $\psi_l = (\eta_h \eta_l + (\eta_h^2 + \eta_l^2)\nu)^{-1}\eta_h$  [23], shown in the dotted rectangle in the bottom of Fig. 1.2. One can refer to [20] and [23] for more details on the composite field S-box architectures. As seen in Fig. 1.2, the above multiplicative inversions consist of composite field multiplications, additions and inversion in the sub-field GF(16). In this figure, the subfield multiplications are shown by crossed circles. Moreover, the circle with plus inside represents  $GF(2^4)$  addition using 4 XOR gates.

# 1.2 The Galois/Counter Mode

Authenticated encryption and decryption are the two functions within the GCM. The authenticated encryption performs two tasks; encrypting the confidential data and com-

Figure 1.2: The composite field S-box architecture using polynomial basis [20] and normal basis [23].

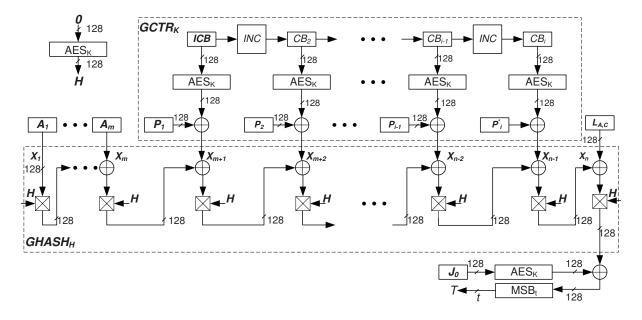

puting an authentication tag. The authenticated decryption function decrypts the confidential data and verifies the tag [5]. The data flow of the authenticated encryption is shown in Fig. 1.3. As seen in this figure, the mechanism for the confidentiality of data is a variation of the block cipher counter mode of operation, denoted by  $GCTR_K$  (Galois Counter with the key K) [5]. For the AES-GCM, the block cipher encryption with the specific key K is shown by  $AES_K$  in Fig. 1.3. Then, the function  $GCTR_K$  performs the block cipher counter mode with the *Initial Counter Block (ICB)* and its increments  $(CB_2 - CB_i)$  and the plaintext blocks  $(P_1 - P_i)$  as the inputs.

As shown in Fig. 1.3, the Galois Hash  $(GHASH_H)$  function within the GCM provides the authentication for the confidential data. This function is constructed by  $GF(2^{128})$ multiplications with a fixed parameter, called the hash subkey (H). The  $GHASH_H$ function calculates

$$\sum_{j=1}^{n} X_j H^{n-j+1} = X_1 \cdot H^n \oplus X_2 \cdot H^{n-1} \oplus \ldots \oplus X_n \cdot H,$$

(1.1)

where  $X_1$  to  $X_n$  are the n, 128-bit blocks of the input [5]. It is noted that the hash subkey

Figure 1.3: The GCM authenticated encryption data flow [5].

is generated by applying the AES to the zero block, i.e.,  $0 = (0, 0, ..., 0) \in GF(2^{128})$ . Then, the  $GHASH_H$  function calculates (1.1) [5]. All the arithmetic operations in (1.1), i.e., additions, GF multiplications, and exponentiations are performed over  $GF(2^{128})$ constructed by the irreducible polynomial  $P(x) = x^{128} + x^7 + x^2 + x + 1$ . As seen in Fig. 1.3, the total number of input blocks to  $GHASH_H$  is n = m + i + 1, where m and i are the number of blocks for the additional authenticated data  $(A_1 - A_m)$  and the output of  $GCTR_K$ , respectively. Eventually, the authentication tag T with length of t bits is derived. In the authenticated decryption, the same  $GHASH_H$  procedure is performed on the authenticated data and ciphertext blocks to verify the tag. For the entire description of the GCM, one can refer to [5] and Algorithms 1 and 2.

Algorithm 1 shows the GCM authenticated encryption [5]. In this algorithm, IV is the Initialization Vector, P is the Plaintext, A is the Additional Authenticated Data, and Kis the Key. It is noted that the authentication in the GCM is performed based on the hash function  $GHASH_H$ . After deriving  $J_0$ ,  $GHASH_H$  is applied to  $(A||0^v||C||0^u||[len(A)]_{64}||$  $[len(C)]_{64}$ ) to obtain block S, from which the authentication tag T with length of t is derived.

Algorithm 2 depicts the GCM authenticated decryption [5]. This algorithm uses the same functions as Algorithm 1, in which another authentication tag (T') is derived. Al-

#### **Algorithm 1** The Authenticated Encryption GCM- $AE_K(IV, P, A)$

1: Let  $H = CIPH_K(0^{128})$ . 2: Define a block,  $J_0$ , as follows: If len(IV)96, let  $IV || 0^{31} || 1.$ then  $J_0$ == If  $len(IV) \neq 96$ , then let s = 128 [len(IV)/128] - len(IV), and let  $J_0 = GHASH_H(IV || 0^{s+64} || [len(IV)]_{64}).$ 3: Let  $C = GCTR_K(inc_{32}(J_0), P)$ . 4: Let  $u = 128\lceil len(C)/128 \rceil - len(C)$  and  $v = 128\lceil len(A)/128 \rceil - len(A)$ . 5: Define a block, S, as follows:  $S = GHASH_H(A||0^v||C||0^u||[len(A)]_{64}||[len(C)]_{64}).$ 6: Let  $T = MSB_t(GCTR_K(J_0, S)).$ 7: Return (C, T).

#### Algorithm 2 The Authenticated Decryption GCM- $AD_K(IV, C, A, T)$

1: If the bit lengths of IV, A or C are not supported, or if  $len(T) \neq t$ , then return FAIL. 2: Let  $H = CIPH_K(0^{128})$ . 3: Define a block,  $J_0$ , as follows:  $IV \| 0^{31} \| 1.$ If len(IV)=96, then let  $J_0$ = If  $len(IV) \neq 96$ , then let  $s = 128 \lceil len(IV)/128 \rceil - len(IV)$ , and let  $J_0 = GHASH_H(IV || 0^{s+64} || [len(IV)]_{64}).$ 4: Let  $P = GCTR_K(inc_{32}(J_0), C)$ . 5: Let  $u = 128\lceil len(C)/128 \rceil - len(C)$  and  $v = 128\lceil len(A)/128 \rceil - len(A)$ . 6: Define a block, S, as follows:  $S = GHASH_H(A||0^v||C||0^u||[len(A)]_{64}||[len(C)]_{64}).$ 7: Let  $T' = MSB_t(GCTR_K(J_0, S)).$ 8: If T = T', return P otherwise return FAIL.

gorithm 2 performs the verification of authenticity by checking if the sent authentication tag T is the same as T'.

# 1.3 Motivation

Using the AES, the sender and the receiver of the sensitive data share a secret key to ensure the confidentiality of the information. Nonetheless, a malicious attacker can take over the secret key and compromise the standard. One of the methods for extracting the side-channel information is the fault attacks for which several approaches have been introduced, see, for instance, [27], [28], [29], [30], [31], [32], and [33]. It is noted that the internal hardware failures may also result in malfunctioning of the AES encryption/decryption. This has been the motivation for the first contribution of this thesis to develop high-performance and low-overhead fault detection schemes for the AES.

Different GCM architectures have been presented in the literature, the details of which are provided throughout this thesis. These methods of realization mostly need many clock cycles to execute, reducing the performance of the GCM architectures and resulting in low throughput. This has been a motivation for the second contribution of this thesis to propose high-performance parallel methods for obtaining the GCM and developing efficient structures for the AES-GCM. The proposed methods are suitable for high-performance applications.

## 1.4 Thesis Outline

The rest of this thesis is organized as follows. In Chapter 2, we review some of the existing works in the literature. In Chapter 3, different AES S-boxes are evaluated and benchmarked in terms of area, delay, and simulation-based power consumption. In Chapter 4, a high-performance fault detection scheme for the composite field S-boxes and inverse S-boxes of the AES is presented and benchmarked. Chapter 5 presents a concurrent low-overhead fault detection method for the AES with emphasis on burst fault detection. In Chapter 6, a structure-independent fault detection approach for the entire AES encryption and decryption is presented. Chapter 7 covers the proposed high-performance parallel hardware architecture for the AES-GCM. Finally, in Chapter 8, we summarize our contributions.

# Chapter 2 Literature Review

HIS chapter presents some previous works on both fault detection and hardware implementations of the AES-GCM.

## 2.1 Fault Detection Schemes

Several fault detection schemes have been proposed to date to counteract the fault attacks and detect the natural faults in cryptographic algorithms and the AES, see, for example, [34], [35], [36], [37], [38], [39], [40], [41], [42], [43], [44], [45], [46], [47], [48], [49], [50], and [51].

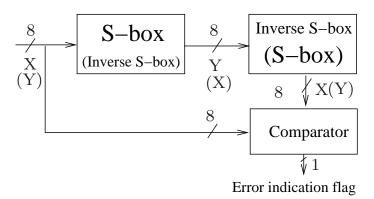

For fault detection of the encryption or decryption in AES one may use redundant units [34], [42], where algorithm-level, round-level and operation-level concurrent error detection for the AES are used. In the algorithm-level, comparing the plain text with the output of a decryption after an encryption is proposed. The round-level error detection uses similar ideas in the rounds, where, the output of a round in encryption is applied to a round in decryption and is compared with the input. The operation-level (or transformation-level) error detection uses the inversion of a transformation in each round and compares the output with the input. Fig. 2.1 shows the operation-level concurrent error detection for S-box and inverse S-box presented in [34]. In this figure, the 8-bit input X of the S-box (8-bit input Y of the inverse S-box) is compared with the output of two consecutive transformations, S-box and inverse S-box (inverse S-box and S-box) using an 8-bit comparator to generate the error indication flag.

There exist a number of fault detection schemes based on the error detecting codes, see, for example, [35], [36], [37], [38], [39], [40], and [41]. Using one parity bit for each

Figure 2.1: Redundant unit fault detection structure for S-box (inverse S-box) [34], [42].

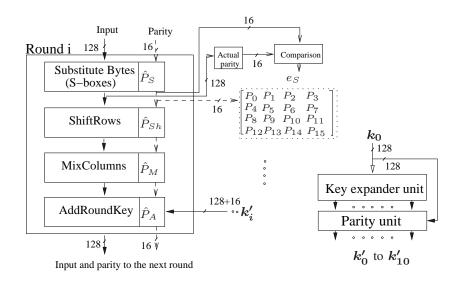

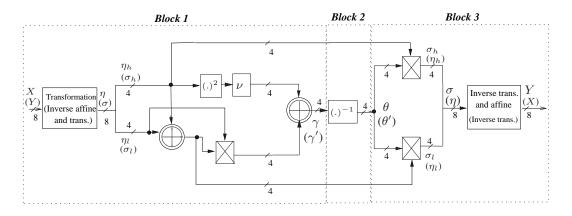

byte of a transformation, one can obtain the structure shown in Fig. 2.2 for the round  $i, 1 \leq i \leq 9$ , of the encryption of the AES-128 (128-bit key) to achieve a parity-based fault detection scheme. Similar structure can be obtained for the AES-128 decryption. The AES-128 encryption/decryption has 10 consecutive rounds which are similar except for the last one in which one of the transformations is not used. As seen in Fig. 2.2, the output parity bits of each transformation in every round of the AES encryption are predicted from the inputs using the prediction boxes denoted by  $\hat{P}$  notations. Then, the comparisons between the predicted parities (shown by a matrix with 16-bit entries) and the actual parities (obtained using the actual parity block) in Fig. 2.2 can be scheduled so that the desired fault detection capability is obtained.

Parity predictions of ShiftRows, InvShiftRows, and AddRoundKey are straightforward and those of MixColumns and InvMixColumns can be done using the equations given in [35], [36], [40], and [41]. It is noted that the parity predictions of the S-box and the inverse S-box proposed in [36] are based on LUTs implementations in which  $512 \times 9$ memory cells are used to generate the predicted parity bit as well as the 8-bit output. In Fig. 2.2, let  $k_0$  be the 128-bit input key to the key expander. Then, all the modified keys, i.e.,  $k'_i$ ,  $0 \le i \le 10$ , consist of the 128-bit expanded key  $k_i$  and 16-bit parities, if one bit parity is used for each byte.

The parity-based scheme proposed in [35] is one of the first fault detection schemes and has received attention in the literature. Although the approach in [35] is a good scheme in terms of the fault detection capability, it has two drawbacks. First, this approach

Figure 2.2: Parity-based fault detection structure of the  $i_{th}$  round in the AES-128 encryption.

is based on using the expanded S-boxes and inverse S-boxes for parity predictions, i.e., two blocks of  $256 \times 9$  memory cells. Not only does this restrict the AES encryption and decryption implementations to LUT-based S-boxes and inverse S-boxes, but it has the area overhead of greater than 100% for either the S-box or the inverse S-box. The second drawback of the approach in [35] is the relatively high area complexity of the parity predictions of MixColumns in the AES encryption. For the AES decryption, the area complexity of the predicted parities of InvMixColumns is even more [36].

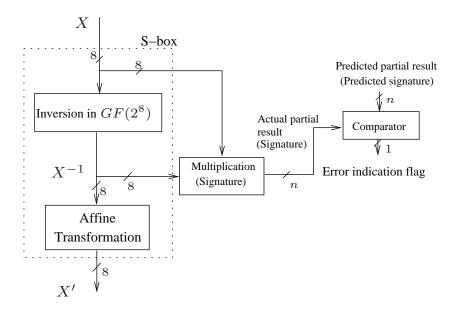

In [37] and [39], instead of using one parity bit or two signatures in case of using the scheme presented in [38] for each byte, one bit parity is used for 128-bit data using the LUT S-boxes. The multiplication-based fault detection scheme [38] for the multiplicative inversion of the S-box is shown in Fig. 2.3. In this scheme, the 8-bit input of the multiplicative inversion is multiplied by the 8-bit output and the *n*-bit result,  $1 \le n \le 8$ , of the multiplication is compared with the *n*-bit actual result, i.e.,  $1 \in GF(2^8)$  if  $X \ne 0$  and  $0 \in GF(2^8)$  if X = 0. Because the multiplicative inversion is also used in the inverse S-box, the same scheme can be used for the inverse S-box.

The schemes presented in [34] and [42] use the redundant unit fault detection approach. It is noted that this results in the area, power, and delay overheads of approximately 100%. In addition, the scheme in [43] proposes using the transformations in an AES round twice for the same data to detect the transient errors. In [44], a concurrent

Figure 2.3: The multiplication-based scheme for the fault detection of the multiplicative inversion [38].

fault detection scheme based on the merged S-box and inverse S-box is proposed. It is also noted that the scheme presented in [49] uses double-data-rate computation for counteracting the fault attacks. Additionally, a fault detection scheme based on the Hamming and Reed-Solomon codes for protecting the storage elements within the AES is proposed in [50]. Furthermore, for the logic elements, the scheme in [36] and the use of the partial duplication of the most vulnerable elements are proposed in [50]. Moreover, the approach in [51] is based on implementing functional redundancy in the AES.

There exist a number of fault detection approaches which are specific to composite field S-boxes and inverse S-boxes, see, for example, [52], [53], [54], [55], and [56]. In the scheme of [52], the fault detection of the multiplicative inversion of the S-box is considered for two specific composite fields. The transformation and affine matrices are excluded in this approach. Moreover, in [53], predicted parities have been used for the multiplicative inversion of a specific S-box using composite field and polynomial basis. Furthermore, the transformation matrices are also considered. In [54], [55], and [56], the composite field S-boxes and inverse S-boxes (using polynomial basis) have been divided into sub-blocks and parity predictions are used for their fault detection. Moreover, FPGA implementations have been performed in [56] to benchmark the presented method. It is noted that the approaches in [55] and [56] (for single fault detection) have been extended

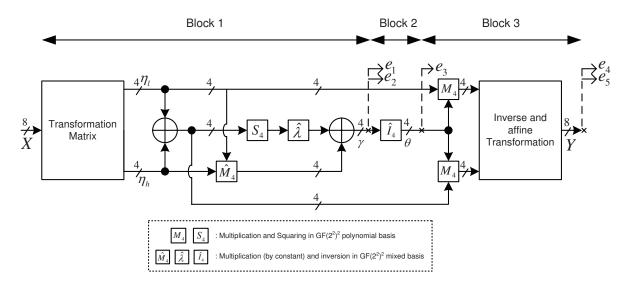

Figure 2.4: Low-power S-box (resp. inverse S-box) architecture using composite fields and polynomial basis [13].

in the work in [57]. This work presents new structures for the S-box and the inverse S-box with higher complexities compared to the original structures for detecting 100% of single faults. We note that unlike the schemes presented in [55] and [56], this work focuses on the stuck-at faults injected not only at the outputs but at any net in the circuit. The results in [57] have been benchmarked using ASIC platform.

# 2.2 AES-GCM Architectures

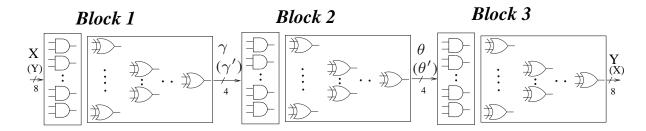

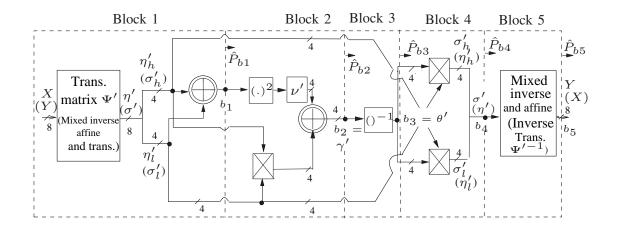

As mentioned in the previous chapter, the S-boxes and the inverse S-boxes are the only nonlinear transformations in the AES, whose hardware implementations affect that of the AES significantly. A low-power implementation of the S-box (resp. inverse S-box) has been presented in [13] which uses the composite field in [20]. For reaching a lowpower architecture with acceptable hardware complexity, it is suggested in [13] that the structures are partitioned into three blocks (see Fig. 2.4). Then, the logic gates within each of these blocks are implemented using two-level logics consisting of the arrays of ANDs and XORs. Although this method increases the area of the composite fields implementation, it reduces the power consumption significantly [13].

The AND-XOR structure of each block shown in Fig. 2.4 results in the low number of transitions and thus low power consumption. This is because the AND array has 50% propagation probability of signal transitions. In [13], similar to many other publications such as [17], [18], [20], and [22], the irreducible polynomials  $u^2 + u + \nu$  and  $v^2 + v + \Phi$ , where  $\nu = \{1100\}_2$  and  $\Phi = \{10\}_2$ , are used for the composite fields. As seen in Fig. 2.4, for block 1, a field element X for the S-box (Y for the inverse S-box) in the binary field  $GF(2^8)$  is converted to the corresponding representation in the composite

Figure 2.5: The sequential method used in [64], [65], and [66] for the hardware implementation of the  $GHASH_H$ .

field  $GF(2^8)/GF(((2^2)^2)^2)$ . The output of block 1 is then obtained as  $\gamma \in GF(2^4)$  $(\gamma' \in GF(2^4)$  for the inverse S-box). As seen in Fig. 2.4,  $\theta \in GF(2^4)$  ( $\theta' \in GF(2^4)$  for the inverse S-box) is then derived as the output of block 2. Eventually, using the irreducible polynomials  $u^2 + u + \nu$  and  $v^2 + v + \Phi$ , the output of the S-box, i.e., Y(X for the inverse S-box), is obtained after conversion from the composite field  $GF(2^8)/GF(((2^2)^2)^2)$  to the binary field  $GF(2^8)$ .

In some previous works such as [13], [20], [22], [27], and [58], one specific S-box and in [59], three reported S-boxes have been synthesized on ASIC. However, exhaustive search has not been performed for all suitable composite fields to evaluate their performance metrics using the same technology. It is also noted that in some other works, see, for instance, [23], [24], [30], [60], [61], and [62], the hardware and timing complexities of different composite field S-boxes have been evaluated in terms of logic gates (in [63], software implementations have been performed). However, benchmarking the performance (including power consumptions through simulation-based approaches) of the S-boxes implementations on hardware platforms has not been performed in these works.

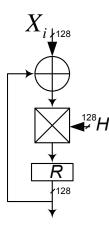

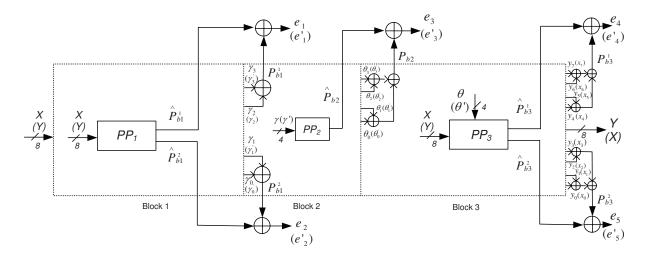

Different GCM architectures have been presented in the literature. In [64], [65], and [66], the sequential method for the hardware implementation of the GCM function is adopted. The sequential method is shown in Fig. 2.5, where one GF multiplier, a set of 128 XOR gates, and a 128-bit register (R) are utilized to perform the operation. Let the register R in Fig. 2.5 be cleared initially. Let n be the number of input blocks to

the  $GHASH_H$  function, i.e.,  $X_i$ ,  $1 \le i \le n$ . Then, after *n* clock cycles, register *R* in Fig. 2.5 contains the result. Although this method of realization is area-efficient, it needs many clock cycles (equal to the number of input blocks), reducing the performance of the architecture.

Because of the low throughput of the sequential method, a parallel method is proposed in [67] which uses two  $GF(2^{128})$  multipliers to perform this operation in parallel. This parallel implementation has been generalized in [68] and [69] so that  $q, q \ge 2$ , parallel  $GF(2^{128})$  multiplications are performed concurrently. In the most efficient method in [68] and [69], for the case of q = 4 and n = 8, the operation in the GCM is realized according to the following calculation steps:

$$\underbrace{\overbrace{(X_1H^4 \oplus X_5)H^4}^{j=1} \times 1 \times 1 \oplus \overbrace{(X_2H^4 \oplus X_6)H}^{j=1} \times H \times H \oplus}_{j=2\dots}}_{j=4} \xrightarrow{j=4} \underbrace{\overbrace{(X_3H^4 \oplus X_7)H}^{j=1} \times H \times 1 \oplus \underbrace{(X_4H^4 \oplus X_8)H}_{j=2\dots} \times 1 \times 1,} (2.1)$$

where all operations are performed over  $GF(2^{128})$  constructed by the irreducible polynomial  $P(x) = x^{128} + x^7 + x^2 + x + 1$  and  $\bigoplus$  comprises 128 XOR gates. Consecutive GF multiplications with H are performed for deriving the powers of the hash subkey used.

Recently, a high-performance approach for computing the  $GHASH_H$  function for long messages has been proposed in [70]. However, in this scheme the hardware complexity is increased. Therefore, a high-performance parallel method for obtaining the GCM by relying on the low-complexity powers of the hash subkey is needed so that without pre-computing the hash subkey exponents, compact realizations of these exponents are obtained and implemented. This results in high-throughput and low-latency GCM hardware architectures, suitable for high-performance applications.

# Chapter 3

# Performance Evaluations and Comparisons of the AES S-boxes

In this chapter, different ASIC architectures of building blocks of the AES S-boxes, the only nonlinear AES transformation, are evaluated and optimized to identify highperformance and low-power architectures. We evaluate the performance of more than 40 S-boxes utilizing a fixed benchmark platform in 65-nm CMOS technology. To obtain the least-complexity S-box, the formulations for the Galois Field (GF) sub-field inversions in  $GF(2^4)$  are optimized. By conducting exhaustive simulations for the input transitions, we analyze the average and peak power consumptions of the AES S-boxes considering the switching activities, gate-level netlists, and parasitic information.

In this chapter, we logic-gate optimize and perform comprehensive ASIC syntheses of more than 40 different S-boxes for deriving their performance metrics. This benchmarking, which is done on the same platform, results in having a clear picture of the performance metrics of different designs. We synthesize the structures of different AES S-boxes using the Synopsys<sup>®</sup> Design Vision<sup>®</sup> (which is the graphical user interface to Synopsys<sup>®</sup> Design Compiler<sup>®</sup>) [73] in STM 65-nm CMOS standard technology [74]. Then, the areas and delays of these hardware architectures are derived and compared. To achieve the least dynamic power-consuming AES S-box, we obtain the average and peak power consumptions of the S-boxes through exhaustive searches considering the possible input transitions. These derivations are based on a timing simulation-based analysis using the switching activities of internal nodes with Synopsys<sup>®</sup> PrimeTime<sup>®</sup> PX [73] and ModelSim<sup>®</sup> [75].

The implementation complexities of the S-boxes using composite fields are dependent

on the choice of the coefficients  $\nu \in GF(2^4)$  and  $\Phi \in GF(2^2)$  in the irreducible polynomials  $u^2+u+\nu$  and  $v^2+v+\Phi$  used for the composite fields, respectively. The composite fields  $GF(((2^2)^2)^2)$  in polynomial basis use iterations to construct the S-box. For these composite fields, the constants  $\nu \in GF(2^4)$  and  $\Phi \in GF(2^2)$  are over  $GF((2^2)^2)/v^2 + v + \Phi$  and  $GF(2^2)/x^2+x+1$ , respectively. According to [24], after exhaustive search for finding the possible choices for  $\nu \in GF(2^4)$  and  $\Phi \in GF(2^2)$ , the following 16 combinations are obtained:  $\Phi \in \{\{10\}_2, \{11\}_2\}$  and  $\nu \in \{\{1000\}_2, \{1001\}_2, \{1010\}_2, \{1011\}_2, \{1100\}_2, \{1101\}_2, \{1101\}_2, \{1110\}_2, \{1111\}_2\}$ . Similarly, for normal basis, it can be derived that the only two acceptable values for  $\Phi$  are  $\Phi = \{10\}_2$  and  $\Phi = \{01\}_2$ . The following 8 values of  $\nu$  are acceptable:  $\nu \in \{\{0100\}_2, \{0001\}_2, \{1000\}_2, \{0010\}_2, \{0111\}_2, \{1011\}_2, \{1110\}_2, \{1110\}_2\}$ .

Based on the possible values of  $\nu$  and  $\Phi$  in polynomial basis representation, the (inverse) transformation matrices can be constructed using the algorithm presented in [22]. In this algorithm, using an exhaustive search, the transformation matrix is constructed using eight base elements in  $GF(((2^2)^2)^2)$ , i.e.,  $1, \xi, \xi^2, \ldots, \xi^7$ , to which eight base elements of  $GF(2^8)$  are mapped. We note that for each combination of  $\nu$  and  $\Phi$ , there exist eight possible (inverse) transformation matrices. These are constructed according to the base element  $\xi$  and the conjugates of this base element, i.e.,  $\xi^{2^i}$ ,  $i = 1, 2, \ldots, 7$ . In what follows, for each combination of  $\nu$  and  $\Phi$ , one of these possible matrices is considered. As suggested in [22], we have also used subexpression sharing for obtaining the low-complexity implementations for these matrices. We note that different (inverse) transformation matrices in normal basis are derived simply by reordering the columns.

The organization of this chapter is as follows. In Section 3.1, logic-gate optimizations for the inversions in  $GF(2^4)$  within the S-boxes are presented. In Section 3.2, we present the results of our syntheses for different S-boxes. Power consumption derivations and comparisons of the S-boxes through a simulation-based method are presented in Section 3.3. The results presented in this chapter can also be found in [71] and [72].

### 3.1 Logic-gate Optimizations

In this section, first we present the architecture of the low-complexity S-box using normal basis. The previously presented low-complexity S-box using normal basis [23] is improved and the hardware complexity of the inversion in  $GF(2^4)$  is reduced.

#### Chapter 3

Let  $\gamma = (\gamma_3, \gamma_2, \gamma_1, \gamma_0)$  be the input and  $\theta = (\theta_3, \theta_2, \theta_1, \theta_0)$  be the output of an inverter in  $GF(2^4)$  using normal basis. Then, the formulations for the inversion in  $GF(2^4)$  using the low-complexity normal basis ( $\Phi = \{10\}_2$ ) presented in [23] are obtained as follows

$$\theta_{3} = \gamma_{2}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{2}\gamma_{1} + \gamma_{1} + \gamma_{0},$$

$$\theta_{2} = \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{2}\gamma_{1} + \gamma_{2}\gamma_{0} + \gamma_{0},$$

$$\theta_{1} = \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{3}\gamma_{0} + \gamma_{3} + \gamma_{2},$$

$$\theta_{0} = \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{1} + \gamma_{3}\gamma_{0} + \gamma_{2}\gamma_{0} + \gamma_{2},$$

(3.1)

where, "+" represents the modulo-2 addition which uses an XOR gate in hardware.

Considering the formulations above, we present the following lemma for reaching a low-complexity architecture of an inverter in  $GF(2^4)$ .

**Lemma 3.1** The low-complexity formulations for the inversion in  $GF(2^4)$  using normal basis can be written as follows.

$$\theta_{3} = (\gamma_{2}\gamma_{1} \vee \gamma_{0}) + \overline{\gamma_{3}}\gamma_{1},$$

$$\theta_{2} = \gamma_{0}(\gamma_{1} \vee \overline{\gamma_{2}}) \vee \gamma_{1}(\gamma_{2} + \gamma_{3}),$$

$$\theta_{1} = (\gamma_{3}\gamma_{0} \vee \gamma_{2}) + \gamma_{3}\overline{\gamma_{1}},$$

$$\theta_{0} = \gamma_{2}(\gamma_{3} \vee \overline{\gamma_{0}}) \vee \gamma_{3}(\gamma_{1} + \gamma_{0}),$$

(3.2)

where, "+" and " $\vee$ " represent the XOR and OR operations, respectively.

**Proof** For having low-complexity structures for  $\theta_3$  and  $\theta_1$ , we use the fact that for two Boolean variables x and y, we have

$$x + y + xy = x \lor y. \tag{3.3}$$

Then, using  $\theta_3$  in (3.1) and considering  $x = \gamma_2 \gamma_1$  and  $y = \gamma_0$  in (3.3), one can find

$$\theta_{3} = \gamma_{2}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{2}\gamma_{1} + \gamma_{1} + \gamma_{0}\theta_{3}$$

=  $(\gamma_{2}\gamma_{1} \vee \gamma_{0}) + \gamma_{1}(\gamma_{3} + 1)$

=  $(\gamma_{2}\gamma_{1} \vee \gamma_{0}) + \overline{\gamma_{3}}\gamma_{1}.$  (3.4)

Similarly, one can consider  $x = \gamma_3 \gamma_0$  and  $y = \gamma_2$  in (3.3) for  $\theta_1$  in (3.1) to obtain

$$\theta_{1} = \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{3}\gamma_{0} + \gamma_{3} + \gamma_{2}$$

$$= (\gamma_{3}\gamma_{0} \lor \gamma_{2}) + \gamma_{3}(\gamma_{1} + 1)$$

$$= (\gamma_{3}\gamma_{0} \lor \gamma_{2}) + \gamma_{3}\overline{\gamma_{1}}.$$

(3.5)

#### Chapter 3

We now prove the formulations for  $\theta_2$  and  $\theta_0$ . According to (3.1) and noting that  $\gamma_i + 1 = \overline{\gamma_i}$ , we obtain

$$\theta_{2} = \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{2}\gamma_{1} + \gamma_{2}\gamma_{0} + \gamma_{0}$$

$$= \gamma_{1}(\gamma_{2} + \gamma_{3}(\gamma_{0} + 1)) + \gamma_{0}(\gamma_{2} + 1)$$

$$= \gamma_{1}(\gamma_{2} + \gamma_{3}\overline{\gamma_{0}}) + \gamma_{0}\overline{\gamma_{2}}.$$

(3.6)

By the definition of the XOR we have  $\gamma_2 + \gamma_3 \overline{\gamma_0} = \overline{\gamma_2} \gamma_3 \overline{\gamma_0} \vee \gamma_2 (\overline{\gamma_3} \vee \gamma_0)$ . Then, (3.6) can be written as

$$\theta_{2} = \gamma_{1}(\overline{\gamma_{2}}\gamma_{3}\overline{\gamma_{0}} \lor \gamma_{2}(\overline{\gamma_{3}} \lor \gamma_{0})) + \gamma_{0}\overline{\gamma_{2}}$$

$$= (\gamma_{1}\gamma_{2}\overline{\gamma_{3}} \lor \gamma_{2}\gamma_{1}\gamma_{0} \lor \gamma_{3}\overline{\gamma_{2}}\gamma_{1}\overline{\gamma_{0}}) + \gamma_{0}\overline{\gamma_{2}}.$$

(3.7)

It is noted that for having a low-complexity structure for  $\theta_2$ , we use the fact that for two Boolean variables x and y, one can prove that

$$x + \overline{x}y = x \lor y. \tag{3.8}$$

Then, by distributing the XOR in (3.7) and using (3.8), the following terms are obtained

$$\gamma_3 \overline{\gamma_2} \gamma_1 \overline{\gamma_0} + \gamma_0 \overline{\gamma_2} = \overline{\gamma_2} (\gamma_3 \gamma_1 \overline{\gamma_0} + \gamma_0) = \overline{\gamma_2} (\gamma_3 \gamma_1 \vee \gamma_0), \tag{3.9}$$

$$\gamma_2 \gamma_1 \gamma_0 + \gamma_0 \overline{\gamma_2} = \gamma_0 (\gamma_2 \gamma_1 + \overline{\gamma_2}) = \gamma_0 (\overline{\gamma_2} \vee \gamma_1), \qquad (3.10)$$

$$\overline{\gamma_3}\gamma_2\gamma_1 + \gamma_0\overline{\gamma_2} = \overline{\gamma_3}\gamma_2\gamma_1 \vee \gamma_0\overline{\gamma_2}. \tag{3.11}$$

Then, according to (3.7), by ORing (3.9)-(3.11) and noting that  $\overline{\gamma_3}\gamma_2\gamma_1 \vee \gamma_3\overline{\gamma_2}\gamma_1 = \gamma_1(\gamma_2 + \gamma_3)$ , it is straightforward to obtain  $\theta_2$  in (3.2).

We obtain the following for  $\theta_0$

$$\theta_0 = \gamma_3 \gamma_2 \gamma_1 + \gamma_3 \gamma_1 + \gamma_3 \gamma_0 + \gamma_2 \gamma_0 + \gamma_2$$

=  $\gamma_3 (\gamma_0 + \gamma_1 (\gamma_2 + 1)) + \gamma_2 (\gamma_0 + 1)$

=  $\gamma_3 (\gamma_0 + \gamma_1 \overline{\gamma_2}) + \gamma_2 \overline{\gamma_0}.$  (3.12)

By the definition of the XOR for  $\gamma_0 + \gamma_1 \overline{\gamma_2}$ , (3.12) can be written as

$$\theta_{0} = \gamma_{3}(\overline{\gamma_{2}}\gamma_{1}\overline{\gamma_{0}} \vee \gamma_{0}(\overline{\gamma_{1}} \vee \gamma_{2})) + \gamma_{2}\overline{\gamma_{0}}$$

=  $(\gamma_{3}\gamma_{0}\overline{\gamma_{1}} \vee \gamma_{3}\gamma_{2}\gamma_{0} \vee \gamma_{3}\overline{\gamma_{2}}\gamma_{1}\overline{\gamma_{0}}) + \gamma_{2}\overline{\gamma_{0}}.$  (3.13)

Then, by distributing the XOR in (3.13) and using (3.8), the following terms are obtained

$$\gamma_3 \overline{\gamma_2} \gamma_1 \overline{\gamma_0} + \gamma_2 \overline{\gamma_0} = \overline{\gamma_0} (\gamma_3 \gamma_1 \overline{\gamma_2} + \gamma_2) = \overline{\gamma_0} (\gamma_3 \gamma_1 \vee \gamma_2), \tag{3.14}$$

$$\gamma_3\gamma_2\gamma_0 + \gamma_2\overline{\gamma_0} = \gamma_2(\gamma_3\gamma_0 + \overline{\gamma_0}) = \gamma_2(\overline{\gamma_0} \vee \gamma_3), \qquad (3.15)$$

$$\overline{\gamma_1}\gamma_3\gamma_0 + \gamma_2\overline{\gamma_0} = \overline{\gamma_1}\gamma_3\gamma_0 \vee \gamma_2\overline{\gamma_0}.$$

(3.16)

Then, according to (3.13), by ORing (3.14)-(3.16) and noting that  $\overline{\gamma_0}\gamma_3\gamma_1 \vee \gamma_3\overline{\gamma_1}\gamma_0 = \gamma_3(\gamma_1 + \gamma_0)$ , one can obtain  $\theta_0$  in (3.2).

It is noted that for reaching a low-complexity architecture, the formulations in (3.2) can be implemented using only NOR, NAND, and XOR gates as follows

$$\theta_{3} = XOR(NOR(NOR(\overline{\gamma_{2}}, \overline{\gamma_{1}}), \gamma_{0}), NAND(\overline{\gamma_{3}}, \gamma_{1})),$$

$$\theta_{2} = NAND(NAND(\gamma_{0}, NAND(\gamma_{2}, \overline{\gamma_{1}})), NAND(\gamma_{1}, XOR(\gamma_{2}, \gamma_{3}))),$$

$$\theta_{1} = XOR(NOR(NOR(\overline{\gamma_{3}}, \overline{\gamma_{0}}), \gamma_{2}), NAND(\overline{\gamma_{1}}, \gamma_{3})),$$

$$\theta_{0} = NAND(NAND(\gamma_{2}, NAND(\gamma_{0}, \overline{\gamma_{3}})), NAND(\gamma_{3}, XOR(\gamma_{1}, \gamma_{0}))).$$

(3.17)

In what presented above, the field inversion in  $GF(2^4)$  of the most compact composite field in [23] has been modified to decrease its hardware complexity. This field uses normal basis with  $\Phi = \{10\}_2$  and  $\nu = \{0001\}_2$ . Now, we consider polynomial basis to further optimize the S-boxes using polynomial basis. We present the following lemma through which the hardware complexity of the composite field inversion in  $GF(2^4)$  is decreased. This is performed by presenting low-complexity formulations for the inversion in  $GF(2^4)$ through logic-gate minimization. Moreover, these formulations are implemented using NAND, NOR, and XOR gates for reducing the complexity.

**Lemma 3.2** Let  $\gamma = (\gamma_3, \gamma_2, \gamma_1, \gamma_0)$  be the input and  $\theta = (\theta_3, \theta_2, \theta_1, \theta_0)$  be the output of an inverter in  $GF(2^4)$ . Then, the formulations for the low-complexity inversion in  $GF(2^4)$  using polynomial basis with  $\Phi = \{11\}_2$  are as follows:

$$\begin{aligned} \theta_{3} &= \gamma_{2}\overline{\gamma_{3}\gamma_{1}} + \gamma_{3}\gamma_{0}, \\ \theta_{2} &= \gamma_{3}\overline{\gamma_{0}} \lor \gamma_{2}(\gamma_{3} \lor \gamma_{1}), \\ \theta_{1} &= \gamma_{2}\overline{\gamma_{0}} \lor \gamma_{3}\overline{\gamma_{1}}\gamma_{0} \lor \overline{\gamma_{3}}\gamma_{1}\overline{\gamma_{2}}, \\ \theta_{0} &= \gamma_{3} \lor \gamma_{1}\overline{\gamma_{0}} \lor \overline{\gamma_{2}}\gamma_{0}\overline{\gamma_{1}} + \gamma_{1}(\gamma_{2} \lor \gamma_{3}\overline{\gamma_{0}}). \end{aligned}$$

(3.18)

Moreover, for  $\Phi = \{10\}_2$ , one reaches the following:

$$\theta_{3} = \gamma_{2}\overline{\gamma_{3}\gamma_{1}} + \gamma_{3}\overline{\gamma_{0}},$$

$$\theta_{2} = \gamma_{2}\overline{\gamma_{1}} \lor \gamma_{3}(\gamma_{2} \lor \gamma_{0}),$$

$$\theta_{1} = \gamma_{3}\gamma_{1}(\gamma_{2} \lor \gamma_{0}) \lor \gamma_{2}\gamma_{0} + \gamma_{3} + \gamma_{2} + \gamma_{1},$$

$$\theta_{0} = \gamma_{0} \lor \gamma_{2}\overline{\gamma_{3}} \lor \overline{\gamma_{1}}\gamma_{3}\overline{\gamma_{2}} + \gamma_{2}(\gamma_{1} \lor \gamma_{0}\overline{\gamma_{3}}).$$

(3.19)

where "+" and " $\lor$ " represent the XOR and OR operations, respectively.

**Proof** For  $\gamma = (\gamma_3, \gamma_2, \gamma_1, \gamma_0)$  as the input and  $\theta = (\theta_3, \theta_2, \theta_1, \theta_0)$  as the output of an inverter in  $GF(2^4)$ , the formulations for the inversion in  $GF(2^4)$  using the polynomial basis with  $\Phi = \{11\}_2$  and  $\Phi = \{10\}_2$  are obtained as follows, respectively, [24], [22]:

$$\theta_{3} = \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{0} + \gamma_{2},$$

$$\theta_{2} = \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{0} + \gamma_{2}\gamma_{1} + \gamma_{3},$$

$$\theta_{1} = \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{0} + \gamma_{3}\gamma_{1} + \gamma_{2}\gamma_{0} + \gamma_{2}\gamma_{1} + \gamma_{2} + \gamma_{1},$$

$$\theta_{0} = \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{2}\gamma_{1}\gamma_{0} + \gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{0} + \gamma_{2}\gamma_{1} + \gamma_{3} + \gamma_{1} + \gamma_{0},$$

$$(3.20)$$

$$\begin{aligned} \theta_{3} &= \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{0} + \gamma_{3} + \gamma_{2}, \\ \theta_{2} &= \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{0} + \gamma_{2}\gamma_{1} + \gamma_{2}, \\ \theta_{1} &= \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{2}\gamma_{0} + \gamma_{3} + \gamma_{2} + \gamma_{1}, \\ \theta_{0} &= \gamma_{3}\gamma_{2}\gamma_{1} + \gamma_{3}\gamma_{2}\gamma_{0} + \gamma_{3}\gamma_{1}\gamma_{0} + \gamma_{2}\gamma_{1}\gamma_{0} + \gamma_{3}\gamma_{1} + \\ \gamma_{3}\gamma_{0} + \gamma_{2}\gamma_{1} + \gamma_{2} + \gamma_{1} + \gamma_{0}. \end{aligned}$$

(3.21)

One can obtain  $\theta_3$ - $\theta_0$  in (3.18) and (3.19) from those of (3.20) and (3.21), respectively. For performing this, we note that  $\gamma_i + 1 = \overline{\gamma_i}$  and  $\gamma_i + \gamma_j + \gamma_i \gamma_j = \gamma_i \lor \gamma_j$ . For instance, now obtain  $\theta_3$  in (3.18) from that of (3.20) as  $\theta_3 = \gamma_3 \gamma_2 \gamma_1 + \gamma_3 \gamma_0 + \gamma_2 = \gamma_2 (\gamma_3 \gamma_1 + 1) + \gamma_3 \gamma_0 =$  $\gamma_2 \overline{\gamma_3 \gamma_1} + \gamma_3 \gamma_0$ . Using similar methods, one can obtain (3.18). As another example, one can obtain  $\theta_3$  in (3.19) from that of (3.21) as  $\theta_3 = \gamma_3 \gamma_2 \gamma_1 + \gamma_3 \gamma_0 + \gamma_3 + \gamma_2 =$  $\gamma_2 (\gamma_3 \gamma_1 + 1) + \gamma_3 (\gamma_0 + 1) = \gamma_2 \overline{\gamma_3 \gamma_1} + \gamma_3 \overline{\gamma_0}$ . By verifying the 16 combinations of the input  $\gamma$ , same results are obtained for (3.18) and (3.20) ((3.19) and (3.21)).

| Structure              |          | Specifications            | Are         | ea     | Delay [Freq.]     | Thro'put   | Effic.                              |

|------------------------|----------|---------------------------|-------------|--------|-------------------|------------|-------------------------------------|

|                        | Φ        | ν                         | $(\mu m^2)$ | $GE^a$ | (ns) [MHz]        | (Gbps)     | $\left(\frac{Mbps}{\mu m^2}\right)$ |

|                        |          | $1000 [30], [24]^{b}$     | 525.2       | 252.5  | 1.31 [763]        | 6.1        | 11.6                                |

|                        |          | 1000  (proposed, (3.19))  | 518.9       | 249.4  | 1.15 [869]        | 7.0        | $13.5^{3}$                          |

|                        |          | 1001                      | 537.2       | 258.2  | 1.43 699          | 5.6        | 10.4                                |

|                        |          | 1010                      | 535.6       | 257.5  | 1.36 735          | 5.9        | 11.0                                |

|                        |          | 1011                      | 540.8       | 260.0  | 1.43 699          | 5.6        | 10.3                                |

|                        | 10       | $1100 [13], [20], [22]^c$ | 540.3       | 259.7  | 1.37 [730]        | 5.8        | 10.8                                |

|                        |          | 1101                      | 548.6       | 263.7  | 1.34 [746]        | 6.0        | 10.9                                |

|                        |          | 1110                      | 524.7       | 252.3  | 1.40 [714]        | 5.7        | 10.9                                |

|                        |          | 1110 (proposed, (3.19))   | $510.2^{3}$ | 245.2  | 1.25 [800]        | 6.4        | 12.5                                |

| Polynomial             |          | 1111                      | 535.6       | 257.5  | 1.40 [714]        | 5.7        | 10.6                                |

| basis                  |          | 1000                      | 528.3       | 253.9  | 1.39 [719]        | 5.8        | 10.9                                |

|                        |          | 1000  (proposed, (3.18))  | 516.3       | 248.2  | $1.11 \ [900]^3$  | $7.2^{3}$  | $13.9^{2}$                          |

|                        |          | 1001                      | 534.6       | 257.0  | 1.56[641]         | 5.1        | 9.6                                 |

|                        |          | $1010 \ [24]^b$           | 519.0       | 249.5  | 1.42 [704]        | 5.6        | 10.9                                |

|                        |          | 1010  (proposed,  (3.18)) | $498.4^{2}$ | 239.6  | $1.11 \ [900]^3$  | $7.2^{3}$  | $14.4^{1}$                          |

|                        | 11       | 1011                      | 531.0       | 255.2  | 1.45 [690]        | 5.5        | 10.4                                |

|                        |          | 1100                      | 548.1       | 263.5  | 1.49 [671]        | 5.4        | 9.8                                 |

|                        |          | 1101                      | 546.5       | 262.7  | 1.42 [704]        | 5.6        | 9.8                                 |

|                        |          | 1110                      | 542.8       | 260.9  | 1.52 [657]        | 5.3        | 9.7                                 |

|                        |          | 1111                      | 542.9       | 261.0  | 1.52 [657]        | 5.3        | 9.7                                 |

|                        |          | $0001 \ [23]^b$           | 569.4       | 273.7  | 1.59[629]         | 5.0        | 8.8                                 |