## Western University Scholarship@Western

**Electronic Thesis and Dissertation Repository**

3-19-2021 1:30 PM

## Parallel Arbitrary-precision Integer Arithmetic

Davood Mohajerani, The University of Western Ontario

Supervisor: Moreno Maza, Marc, The University of Western Ontario

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree

in Computer Science

© Davood Mohajerani 2021

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the Numerical Analysis and Scientific Computing Commons, and the Theory and Algorithms

Commons

#### **Recommended Citation**

Mohajerani, Davood, "Parallel Arbitrary-precision Integer Arithmetic" (2021). Electronic Thesis and Dissertation Repository. 7674.

https://ir.lib.uwo.ca/etd/7674

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact wlswadmin@uwo.ca.

#### **Abstract**

Arbitrary-precision integer arithmetic computations are driven by applications in solving systems of polynomial equations and public-key cryptography. Such computations arise when high precision is required (with large input values that fit into multiple machine words), or to avoid coefficient overflow due to intermediate expression swell. Meanwhile, the growing demand for faster computation alongside the recent advances in the hardware technology have led to the development of a vast array of many-core and multi-core processors, accelerators, programming models, and language extensions (e.g., CUDA and OPENCL for GPUs, and OPENMP and CILK for multi-core CPUs). The massive computational power of parallel processors makes them attractive targets for carrying out arbitrary-precision integer arithmetic. At the same time, developing parallel algorithms, followed by implementing and optimizing them as multi-threaded parallel programs imposes a set of challenges. This work explains the current state of research on parallel arbitrary-precision integer arithmetic on GPUs and CPUs, and proposes a number of solutions for some of the challenging problems related to this subject.

**Keywords:** Arbitrary-precision integer arithmetic, FFT, GPU, Multi-core

## Summary

Arbitrary-precision integer arithmetic computations are driven by applications in solving systems of polynomial equations and public-key cryptography. Such computations arise when high precision is required. Meanwhile, the growing demand for faster computation alongside the recent advances in the hardware technology have led to the development of a vast array of many-core and multi-core processors, accelerators, programming models, and language extensions. The massive computational power of parallel processors makes them attractive targets for carrying out arbitrary-precision integer arithmetic. At the same time, developing parallel algorithms, followed by implementing and optimizing them as multi-threaded parallel programs imposes a set of challenges. This work explains the current state of research on parallel arbitrary-precision integer arithmetic on GPUs and CPUs, and proposes a number of solutions for some of the challenging problems related to this subject.

## Co-Authorship Statement

- Chapter 2 is a joint work with Liangyu Chen, Svyatoslav Covanov, and Marc Moreno Maza. This work is published in [1]. The contributions of the thesis author include: a new GPU implementation, optimization of arithmetic operations on GPU, experimental results (tables, diagrams, profiling information) for comparing the presented algorithms against computationally equivalent solutions on CPUs and GPUs.

- Chapter 3 is a joint work with Svyatoslav Covanov, Marc Moreno Maza, and Linxiao Wang. This work is published in [2]. The contributions of the thesis author include: adaptation of convolution code (originally developed by Svyatoslav Covanov as part of BPAS library) for multiplying arbitrary elements of big prime field, specialized arithmetic for the CRT, implementation and tuning of base-case DFT functions, parallelization of the code using CILK, and collection of experimental results.

- Chapter 4 is a joint work with Alexander Brandt, Marc Moreno Maza, Jeeva Paudel, and Linxiao Wang. A preprint of this work is published in [3]. The contributions of the thesis author include: processing of the annotated CUDA kernel code, generation of instrumented binary code using the LLVM Pass Framework, development of a customized profiler using NVIDIA's EVENT API within the CUPTI API, and collection of experimental results.

- **Chapter 5** is a joint work with Marc Moreno Maza. The contributions of the thesis author include: algorithm design and analysis, implementation, code optimization and collection of experimental results.

## Acknowlegements

First and foremost, I would like to thank my supervisor Professor Marc Moreno Maza. I am grateful for his advice, support, and providing me the opportunity to work on multiple fascinating problems. Through our discussions, I have had the chance to learn a handful of lessons, including but not limited to, the emphasis on the first principles, clear and concise expression of ideas, and trying to systematically model the problems with algebraic structures. There were multiple times that I assumed a problem could not be further studied, or optimized and more than once I was proven wrong. This in essence has taught me to distinguish the real barriers versus the ones that are a creation of my thinking. Everything that I have worked on has taught me another important lesson that I must always remember and that is what Voltaire once said it best: "Perfect is the enemy of the good."

I am grateful for the insightful comments and questions of thesis examiners Professor Michael Bauer, Professor Mark Daley, Professor Arash Reyhani-Masoleh, and Professor Éric Schost.

I would like to thank the members of Ontario Research Center for Computer Algebra (OR-CCA) and the Computer Science Department of the University of Western Ontario. I am thankful to my colleagues and co-authors; I have learned a little bit of what to do and what not to do from each of you. Specifically, I am thankful to Svyatoslav Covanov for laying the theoretical foundation and further contributions to our joint work on big prime field FFT. I also would like to thank Alexander Brandt for his help with proofreading chapter 5 of this thesis as well as our ISSAC 2019 paper (FFT on multi-core CPUs) although he was not a co-author of that work.

Last but not least, I am very thankful to my family and friends for their endless support.

## **Contents**

| Al | ostra | et                                                           | ii   |

|----|-------|--------------------------------------------------------------|------|

| Su | mma   | ary                                                          | iii  |

| Co | -Aut  | horship Statement                                            | iv   |

| A  | knov  | wlegements                                                   | v    |

| Li | st of | Figures                                                      | viii |

| Li | st of | Tables                                                       | ix   |

| 1  | Intr  | roduction                                                    | 1    |

|    | 1.1   | Background and motivation                                    | 1    |

|    | 1.2   | Challenges and objectives                                    | 2    |

| 2  | Big   | Prime Field FFT on GPUs                                      | 4    |

|    | 2.1   | Introduction                                                 | 4    |

|    | 2.2   | Complexity analysis                                          | 5    |

|    | 2.3   | Generalized Fermat numbers                                   | 8    |

|    | 2.4   | FFT Basics                                                   | 13   |

|    | 2.5   | Blocked FFT on the GPU                                       | 14   |

|    | 2.6   | Implementation                                               | 16   |

|    | 2.7   | Experimentation                                              | 17   |

|    | 2.8   | Conclusion                                                   | 22   |

|    | 2.9   | Appendix: modular methods and unlucky primes                 | 22   |

| 3  | Big   | Prime Field FFT on Multi-core Processors                     | 26   |

|    | 3.1   | Introduction                                                 | 26   |

|    | 3.2   | Generalized Fermat prime fields                              | 28   |

|    | 3.3   | Optimizing multiplication in generalized Fermat prime fields | 29   |

|    | 3.4   | A generic implementation of FFT over prime fields            | 32   |

|    | 3.5   | Experimentation                                              | 37   |

|    | 3.6   | Conclusions and future work                                  | 44   |

| 4  | KLA   | ARAPTOR: Finding Optimal Kernel Launch Parameters            | 45   |

| Curriculum Vitae |     |                                                                   |    |  |  |  |  |  |

|------------------|-----|-------------------------------------------------------------------|----|--|--|--|--|--|

| Bibliography     |     |                                                                   |    |  |  |  |  |  |

| 6 Conclusion     |     |                                                                   |    |  |  |  |  |  |

|                  | 5.8 | Discussion                                                        | 80 |  |  |  |  |  |

|                  | 5.7 | Experimentation                                                   | 75 |  |  |  |  |  |

|                  | 5.6 | Complexity analysis                                               | 70 |  |  |  |  |  |

|                  | 5.5 | A fine-grained parallel multiplication algorithm                  | 69 |  |  |  |  |  |

|                  | 5.4 | Problem definition                                                |    |  |  |  |  |  |

|                  | 5.3 | Choice of algorithm for parallelization                           | 67 |  |  |  |  |  |

|                  | 5.2 | Essential definitions for designing parallel algorithms           |    |  |  |  |  |  |

|                  | 5.1 | Introduction                                                      | 66 |  |  |  |  |  |

| 5                | Arb | itrary-precision Integer Multiplication on GPUs                   | 66 |  |  |  |  |  |

|                  | 4.8 | Conclusions and future work                                       | 64 |  |  |  |  |  |

|                  | 4.7 | Experimentation                                                   |    |  |  |  |  |  |

|                  | 4.6 | The implementation of KLARAPTOR                                   | 59 |  |  |  |  |  |

|                  | 4.5 | Runtime selection of thread block configuration for a CUDA kernel | 57 |  |  |  |  |  |

|                  | 4.4 | An algorithm to build and deploy rational programs                | 55 |  |  |  |  |  |

|                  | 4.3 | KLARAPTOR: a dynamic optimization tool for CUDA                   | 54 |  |  |  |  |  |

|                  | 4.2 | Theoretical foundations                                           | 48 |  |  |  |  |  |

|                  | 4.1 | Introduction                                                      | 45 |  |  |  |  |  |

# **List of Figures**

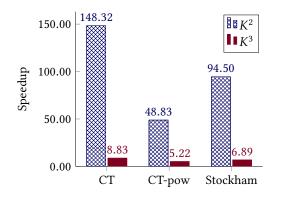

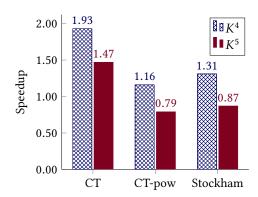

| 2.1 | Speedup diagram for computing the benchmark for a vector of size $N = K^e$ $(K = 16)$ for $P_3 := (2^{63} + 2^{34})^8 + 1$                                                                                                                                                                                                                                                                                                                             | 21 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Speedup diagram for computing the benchmark for a vector of size $N = K^e$                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | $(K = 32)$ for $P_4 := (2^{62} + 2^{36})^{16} + 1$                                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

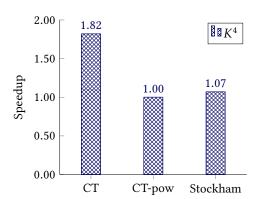

| 2.3 | Running time of computing DFT <sub>N</sub> with $N = K^4$ on a GTX 760M GPU                                                                                                                                                                                                                                                                                                                                                                            | 21 |

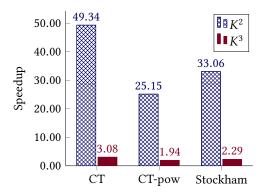

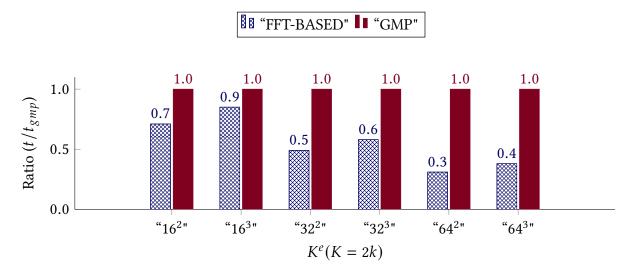

| 3.1 | Ratio $(t/t_{gmp})$ of average time spent in one multiplication operation measured during computation of FFT over $\mathbb{Z}/p\mathbb{Z}$ on vectors of size $N=K^e$                                                                                                                                                                                                                                                                                  | 42 |

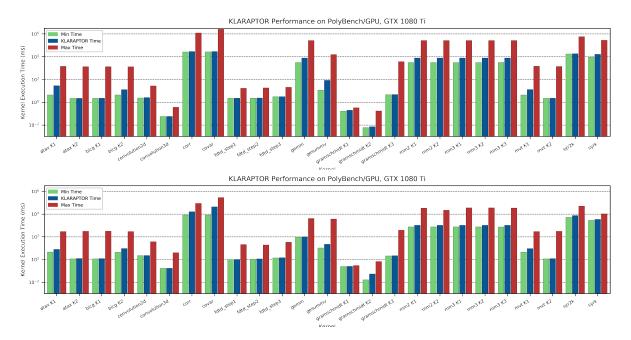

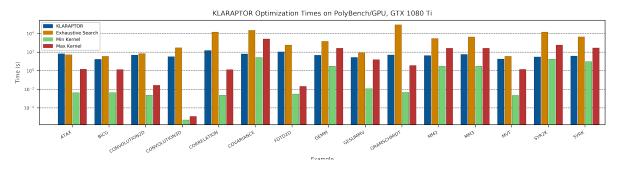

| 4.1 | Comparing kernel execution time (log-scaled) for the thread block configuration chosen by KLARAPTOR versus the minimum and maximum times as determined by an exhaustive search over all possible configurations. Kernels are part of the PolyBench/GPU benchmark suite and executed on (1) a GTX 1080Ti with a data size of $N=8192$ (except convolution3d with $N=1024$ ), and (2) a GTX 760M with a data size of $N=2048$ (except convolution3d with |    |

|     | N=512 and gemm with $N=1024$ )                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

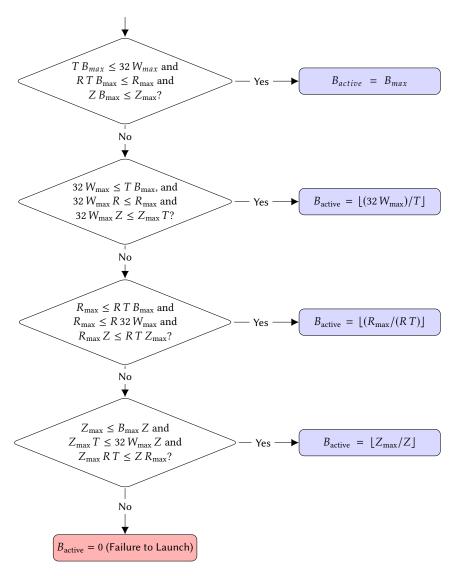

| 4.2 | Rational program (presented as a flow chart) for the calculation of active blocks                                                                                                                                                                                                                                                                                                                                                                      |    |

| 4.3 | in CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52 |

|     | values up to $N=8192$ (except convolution3d with $N=1024$ )                                                                                                                                                                                                                                                                                                                                                                                            | 64 |

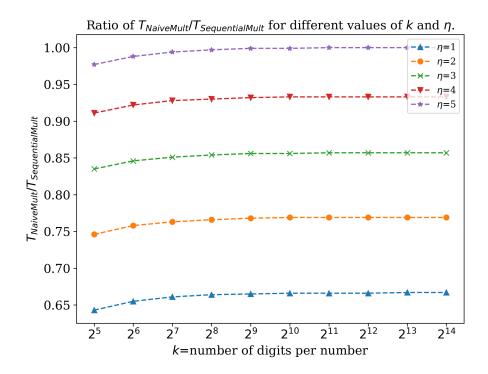

| 5.1 | Estimated running-time ratio for various values of $k$ and $\eta$                                                                                                                                                                                                                                                                                                                                                                                      | 76 |

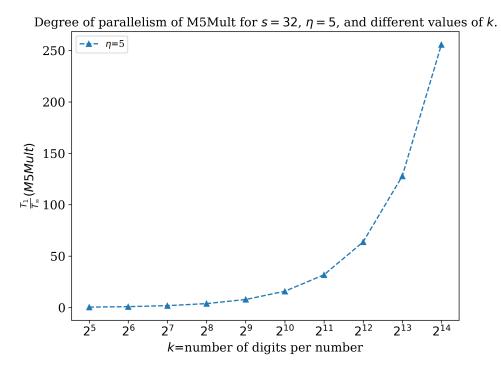

| 5.2 | Estimated degree of parallelism for various values of $k$ with $s=32$ and $\eta=5$ .                                                                                                                                                                                                                                                                                                                                                                   | 76 |

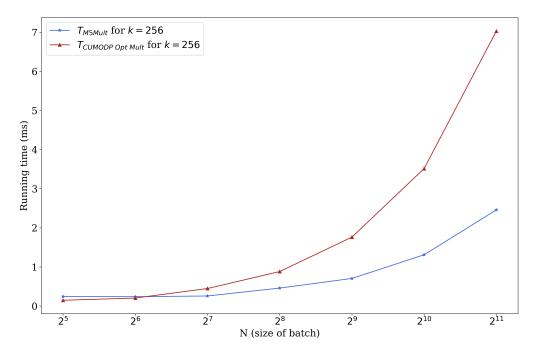

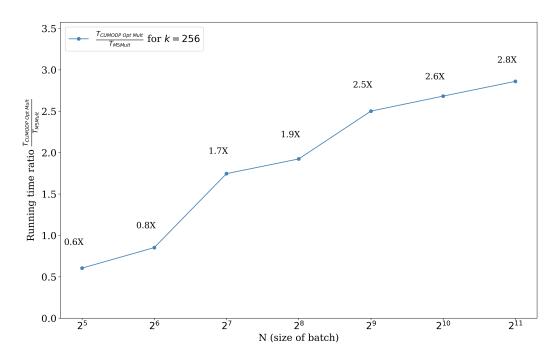

| 5.3 | The average running time (in milliseconds) for computing batches of $k = 256$                                                                                                                                                                                                                                                                                                                                                                          |    |

|     | digit integer multiplications using OptMult and M5Mult                                                                                                                                                                                                                                                                                                                                                                                                 | 77 |

| 5.4 | Comparing ratio of the average running time of OptMult to the average                                                                                                                                                                                                                                                                                                                                                                                  |    |

|     | running time of M5Mult for computing batches of $k = 256$ digit integer                                                                                                                                                                                                                                                                                                                                                                                |    |

|     | multiplications                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78 |

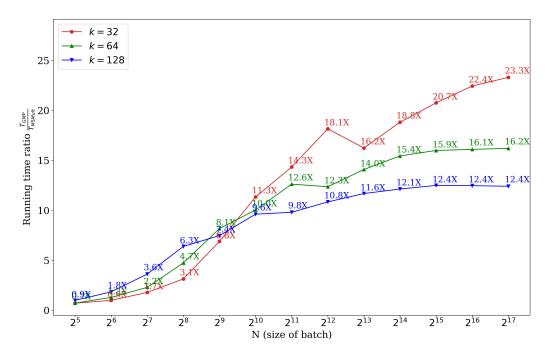

| 5.5 | Comparing the ratio of the running time of GMP to the running time of M5Mult                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | for computing batches of $N$ integer multiplications of $32 \le k \le 128$ digits                                                                                                                                                                                                                                                                                                                                                                      | 79 |

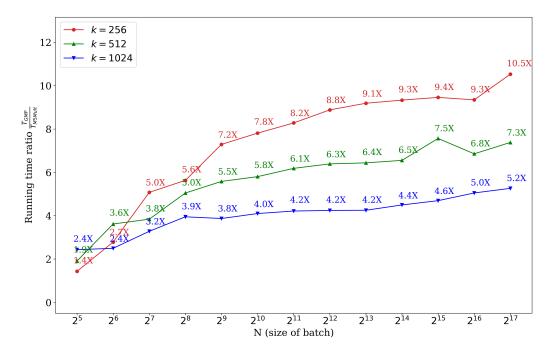

| 5.6 | Comparing the ratio of the running time of GMP to the running time of M5Mult                                                                                                                                                                                                                                                                                                                                                                           |    |

|     | for computing batches of N integer multiplications of $256 \le k \le 1024$ digits                                                                                                                                                                                                                                                                                                                                                                      | 79 |

## **List of Tables**

| 2.1 | SRGFNs of practical interest                                                                                                                                                                                                   | 9  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Running time of computing the benchmark for $N = K^e$ on GPU (timings in milliseconds)                                                                                                                                         | 19 |

| 2.3 | Profiling results for computing base-case $DFT_K$ on a GTX 760M GPU (col-                                                                                                                                                      |    |

| 2.5 | lected using NVIDIA nvprof)                                                                                                                                                                                                    | 20 |

| 2.4 | Definitions of NVIDIA nvprof metrics according to [4]                                                                                                                                                                          | 20 |

| 2.5 | Running time of computing the benchmark for $N = K^e$ using sequential C code on CPU (timings in milliseconds)                                                                                                                 | 22 |

| 2.6 | Speedup ratio $(\frac{T_{\text{CPU}}}{T_{\text{GPU}}})$ for computing the benchmark for $N = K^e$ for $P_3$ and $P_4$ (timings in milliseconds)                                                                                | 22 |

| 3.1 | The set of big primes of different sizes which are used for experimentations                                                                                                                                                   | 39 |

| 3.2 | The running-time of computing $10^6$ modular multiplications in $\mathbb{Z}/p\mathbb{Z}$ for $P_8$ , $P_{16}$ , $P_{32}$ , and $P_{64}$ (measured on Intel-i7-7700K)                                                           | 39 |

| 3.3 | Time (in milliseconds) and percentage (%) of the total time spent in different steps of computing $10^6$ GFPF multiplications of arbitrary elements in $\mathbb{Z}/p\mathbb{Z}$                                                |    |

|     | for primes $P_8$ , $P_{16}$ , $P_{32}$ , and $P_{64}$ (measured on Intel-i7-7700K)                                                                                                                                             | 40 |

| 3.4 | The running-time (in milliseconds) and ratio ( $t_{\text{GFPF}}/t_{\text{GMP}}$ ) of serial and parallel computation of FFT on vectors of size $N=K^e$ over $\mathbb{Z}/p\mathbb{Z}$ for $P_4$ , $P_8$ , $P_{16}$ , $P_{32}$ , |    |

|     | $P_{64}$ , and $P_{128}$ (measured on Intel-i7-7700K)                                                                                                                                                                          | 41 |

| 3.5 | The running-time (in miliseconds) and ratio $(t_{\text{GFPF}}/t_{\text{GMP}})$ of serial and parallel computation of FFT on vectors of size $N=K^e$ over $\mathbb{Z}/p\mathbb{Z}$ for $P_4$ , $P_8$ , $P_{16}$ , $P_{32}$ ,    |    |

|     | $P_{64}$ , and $P_{128}$ (measured on Xeon-X5650)                                                                                                                                                                              | 41 |

| 3.6 | Time spent (milliseconds) in different steps of serial and parallel computation of DFT of size $N=K^3$ over $\mathbb{Z}/p\mathbb{Z}$ , for prime $P_{32}$ ( $K=2k=64$ ) measured on                                            |    |

|     | Intel-i7-7700K                                                                                                                                                                                                                 | 43 |

| 3.7 | Ratio $(t_{serial}/t_{parallel})$ for serial vs. parallel execution of each implementation for $N=K^e$ ( $K=2k$ , $e=3$ ) measured on both Intel-i7-7700K and                                                                  |    |

|     | Xeon-X5650 with and without hyper-threading enabled                                                                                                                                                                            | 43 |

| 4.1 | KLARAPTOR vs. exhaustive search for thread block configuration choice for kernels in Polybench/GPU                                                                                                                             | 63 |

| 5.1 | Comparison of algorithms for multiplying polynomials $f(x)$ , $g(x) \in R[x]$ of                                                                                                                                               |    |

|     | degree less than $k$                                                                                                                                                                                                           | 66 |

| 5.2 | Comparison of algorithms for multiplying $k$ machine word integers                       | 67 |

|-----|------------------------------------------------------------------------------------------|----|

| 5.3 | Relative cost of arithmetic operations                                                   | 71 |

| 5.4 | Profiling results for computing a batch of $N = 2^{10}$ integers of size $k = 256$ dig-  |    |

|     | its using M5Mult with $s=256$ ( $\lambda=\frac{k}{s}=1$ ) collected on NVIDIA GTX1080Ti. | 77 |

| 5.5 | Profiling results for computing a batch of $N = 2^{10}$ integers of size $k = 256$       |    |

|     | digits using OptMult from CUMODP library, collected on NVIDIA GTX1080Ti.                 | 78 |

## 1 Introduction

## 1.1 Background and motivation

Arbitrary-precision integer arithmetic is driven by applications in solving systems of polynomial equations and cryptography. Those arithmetic calculations arise when high precision is required either because of large input values that fit into multiple machine words, or because of possible coefficient overflow due to intermediate expression swell. The main difficulty with the implementation of arbitrary-precision arithmetic is to sharply control hardware resources, which translates in scheduling and parallelization challenges. Meanwhile, the growing demand for faster computation alongside the recent advances in the hardware technology have led to the development of a vast array of many-core and multi-core processors, accelerators, programming models, and language extensions (e.g., CUDA and OpenCL for GPUs, and OpenMP and Cilk for multi-core CPUs). The massive computational power of the parallel processors, specially GPUs, makes them viable targets for carrying out arbitrary-precision integer arithmetic.

At the same time, developing parallel algorithms, followed by implementing and optimizing them as multi-threaded parallel programs imposes a set of challenges. This thesis explains the current state of research on a number of a problems in arbitrary-precision arithmetic on CUDA-enabled GPUs as well as multi-core CPUs, also, proposes a number of solutions for some of the challenging problems related to this subject. The solutions include parallel algorithms, complexity analysis, experimental results, and finally, critical implementation tricks for each problem. Combining the solutions together, the goal is to maximize the performance of arbitrary-precision integer arithmetic on parallel hardware. This work is inspired by the previous research papers, algorithms and software libraries in code generation and optimization such as SPIRAL [5] and FFTW [6, 7], auto-tuning such as ATLAS [8], and the mathematical libraries such as GMP [9], FLINT [10], and NTL [11].

Note that the emphasis on *arbitrary-precision* arithmetic is to distinguish the proposed solutions from the ones for *fixed multi-precision* arithmetic, where the implementation is specifically tuned for numbers that fit in *s* machine words, where *s* is a prescribed and small power of 2, typically between 1 and 8. In our work, this number *s* of machine words is

• either prescribed in advance but the value of s can be arbitrary large, or

• not prescribed in advance, thus implying that, for an arithmetic operation, input and output numbers may use different values of *s*.

In the former case, our arithmetic operations take place in a prime field  $\mathbb{Z}/p\mathbb{Z}$  where p fits into multiple machine words. Meanwhile, in the latter case, we work over the ring  $\mathbb{Z}$  of integers.

## 1.2 Challenges and objectives

In this section, first, we review the common objectives among the subjects that we have studied. Then, we provide a brief summary of the problems and the proposed solutions.

#### Common objectives

The primary objective is an end-to-end optimization effort for better use of the hardware resources. To put it another way, maximizing the performance by minimizing the running time throughout the entire system. To be more specific, the main focus in each of the studied problems is to provide a set of ideas, implementation tricks, and experimental results in the following order of priority:

- to design new algorithms, or to adapt existing ones for parallel architectures,

- to use memory hierarchy efficiently in order to minimize the communication overhead, and finally,

- to apply device-specific optimizations to reach to the peak performance on a device; this includes but not limited to loop unrolling, kernel decomposition, using inline assembly, writing code with respect to the way the hardware works (e.g., taking into account the scheduler, instruction-level parallelism, and pipelining features of the device).

## Big prime field FFT on GPUs

We consider prime fields of large characteristic  $\mathbb{Z}/p\mathbb{Z}$  where p fits on k machine words and k is a power of 2. When the characteristic of these fields is restricted to a subclass of the generalized Fermat numbers, we show that arithmetic operations in such fields offer attractive performance, both in terms of algebraic complexity and parallelism. In particular, these operations can be vectorized, leading to efficient implementation of fast Fourier transforms on graphics processing units. This work demonstrates the potential of GPUs and their huge computational capacity for tackling an essential computational algebra problem, that is, directly computing FFT over large prime fields as a competitive alternative to modular computation of FFT based on the Chinese Remainder Theorem (CRT). We explain more details in Chapter 2.

#### Big prime field FFT on Multi-core

This work extends the previous study realized on GPUs to multi-core processors. In this new context, we overcome the less fine control of hardware resources by successively using FFT in support of the multiplication in those fields. We obtain favorable speedup factors (up to 6.9x on a 6-core, 12 threads node, and 4.3x on a 4-core, 8 threads node) of our parallel implementation compared to the serial implementation for the overall application thanks to the low memory footprint and the sharp control of arithmetic instructions of our implementation of generalized Fermat prime fields. We explain more details in Chapter 3.

## KLARAPTOR: A Tool for Dynamically Finding Optimal Kernel Launch Parameters Targeting CUDA Programs

We present KLARAPTOR (Kernel LAunch parameters RAtional Program estimaTOR), a tool built on top of the LLVM Pass Framework and NVIDIA CUPTI API to dynamically determine the optimal values of kernel launch parameters of a CUDA kernel. We describe a technique to build at the compile-time of a CUDA program a so-called rational program. The rational program, based on some performance prediction model, and knowing particular data and hardware parameters at runtime, can be executed to automatically and dynamically determine the values of launch parameters for the CUDA program that will yield nearly optimal performance. Our underlying technique could be applied to parallel programs in general, given a performance prediction model which accounts for program and hardware parameters. We have implemented and tested our technique in the context of GPU kernels written in CUDA. We explain more details in Chapter 4.

## Arbitrary-precision Integer Multiplication on GPUs

In this work, we propose a new fine-grained parallel algorithm for multiplying arbitrary-precision integers of k digits on. This solution is based on classical  $O(k^2)$  algorithm. We explain more details in Chapter 5.

## 2 Big Prime Field FFT on GPUs

#### 2.1 Introduction

Prime field arithmetic plays a central role in computer algebra by supporting computation in Galois fields. The prime fields that are used in computer algebra systems, in particular in the implementation of modular methods, are often of small characteristic, that is, based on prime numbers that fit in a machine word. Increasing precision beyond the machine word size can be done via the Chinese Remainder Theorem (CRT) or Hensel Lemma. However, using machine-word size, thus small, prime numbers yields major issues in certain modular methods, in particular for solving systems of non-linear equations. Indeed, in such circumstances, the so-called *unlucky primes* are to be avoided, see for instance [12, 13] as well as Section 2.9. This makes using larger primes desirable.

We consider prime fields of large characteristic, typically fitting on k machine words, where k is a power of 2. In practice, k typically ranges from 2 to 1024. When the characteristic of these fields is restricted to a subclass of the generalized Fermat numbers, we show that arithmetic operations in such fields offer attractive performance both in terms of algebraic complexity and parallelism. In particular, these operations can be vectorized, leading to efficient implementation of fast Fourier transforms on graphics processing units (GPUs).

We present algorithms for arithmetic operations in a "big" prime field  $\mathbb{Z}/p\mathbb{Z}$ , where p is a generalized Fermat number of the form  $p = r^k + 1$  where r fits a machine-word and k is a power of 2. We report on a GPU implementation of those algorithms as well as a GPU implementation of a Fast Fourier Transform (FFT) over such a big prime field. Our experimental results show that

- 1. computing an FFT of size N, over a big prime field for p fitting on k 64-bit machinewords, and

- 2. computing 2k FFTs of size N, over a small prime field (that is, where the prime fits a 32-bit half-machine-word) followed by a combination (i.e. CRT-like) of those FFTs

are two competitive approaches in terms of running time. Since the former approach has the advantage of reducing the occurrence of unlucky primes when applying modular methods (in particular in the area of polynomial system solving), we view this experimental observation as a promising result.

The reasons for a GPU implementation are as follows. First, the model of computations and the hardware performance provide interesting opportunities for big prime field arithmetic, in particular in terms of vectorization of the program code. Secondly, highly optimized FFTs over small prime fields have been implemented on GPUs by Wei Pan [14, 15] in the CUMODP library, see www.cumodp.org, and we use them in our experimental comparison.

Section 3.5 reports on various comparative experimentations. First, a comparison of the above two approaches implemented on GPU, exhibiting an advantage for the FFT over a big prime field. Second, a comparison between the two same approaches implemented on a single-core CPU, exhibiting an advantage for the CRT-based FFT over small prime fields. Third, from the two previous comparisons, one deduces a comparison of the FFT over a big prime field (resp. the CRT-based FFT over small prime fields) implemented on GPU and CPU, exhibiting a clear advantage for the GPU implementations. Overall, the big prime field FFT on the GPU is the best approach.

A discrete Fourier transform (DFT) over  $\mathbb{Z}/p\mathbb{Z}$ , when p is a generalized Fermat prime, can be seen as a generalization of the FNT (Fermat number transform), which is a specific case of the NTT (number theoretic transform). However, the computation of a DFT over  $\mathbb{Z}/p\mathbb{Z}$  implies additional considerations, which are not taken into account in the literature on NTT or FNT computations [16, 17].

The computation of a NTT can be done via various methods used for a DFT, among them is the radix-2 Cooley-Tukey, for example. However, the final complexity depends on the way a given DFT is computed. It appears that, in the context of generalized Fermat primes, there is a better choice than the radix-2 Cooley-Tukey. The method used in the present paper is related to the article [18], which is derived from Fürer's algorithm [19] for the multiplication of large integers. The practicality of this latter algorithm is an open question. And, in fact, the work reported in our paper is a practical contribution responding to this open question.

The paper [16] discusses the idea of using Fermat number transform for computing convolutions, thus working modulo numbers of the form  $F = 2^b + 1$ , where b is a power of 2. This is an effective way to avoid round-off error caused by twiddle factor multiplication in computing DFT over the field of complex numbers. The paper [17] considers *generalized Fermat Mersenne* (GFM) prime numbers that prime of the form  $(q^{pn} - 1)/(q - 1)$  where, typically, q is 2 and both p and n are small. These numbers are different from the primes used in our paper, which have the form  $r^k + 1$  where r is typically machine-word long and k is a power of 2 so that r is a 2k-th primitive root of unity, see Section 2.3.

## 2.2 Complexity analysis

Consider a prime field  $\mathbb{Z}/p\mathbb{Z}$  and N, a power of 2, dividing p-1. Then, the finite field  $\mathbb{Z}/p\mathbb{Z}$  admits an N-th primitive root of unity (see Section 2.4 for this notion). Denote by  $\omega$  such an element. Let  $f \in \mathbb{Z}/p\mathbb{Z}[x]$  be of degree at most N-1. Then, computing the DFT of f at  $\omega$  via

an FFT, following the standard 2-way divide-and-conquer algorithm, (see Chapter 8 in [20]) amounts to:

- 1.  $N \log(N)$  additions in  $\mathbb{Z}/p\mathbb{Z}$ ,

- 2.  $(N/2) \log(N)$  multiplications by a power of  $\omega$  in  $\mathbb{Z}/p\mathbb{Z}$ .

If the bit-size of *p* is *k* machine words, then

- 1. each addition in  $\mathbb{Z}/p\mathbb{Z}$  costs O(k) machine-word operations,

- 2. each multiplication by a power of  $\omega$  costs O(M(k)) machine-word operations,

where  $n \mapsto M(n)$  is a multiplication time as defined in [20]. Therefore, multiplication by a power of  $\omega$  becomes a bottleneck as k grows. To overcome this difficulty, we consider the following trick proposed by Martin Fürer in [19, 21]. We assume that  $N = K^e$  holds for some "small" K, say K = 32 and an integer  $e \ge 2$ . Further, we define  $\eta = \omega^{N/K}$ , with  $J = K^{e-1}$  and assume that multiplying an arbitrary element of  $\mathbb{Z}/p\mathbb{Z}$  by  $\eta^i$ , for any  $i = 0, \ldots, K-1$ , can be done within O(k) machine-word operations. Consequently, every arithmetic operation (addition, multiplication) involved in a DFT of size K, using  $\eta$  as a primitive root, amounts to O(k) machine-word operations. Therefore, such DFT of size K can be performed with  $O(K \log(K) k)$  machine-word operations. As we shall see in Section 2.3, this latter result holds whenever p is a so called *generalized Fermat number*.

Returning to the DFT of size N at  $\omega$  and using the factorization formula of Cooley and Tukey, we have

$$DFT_{JK} = (DFT_J \otimes I_K)D_{J,K}(I_J \otimes DFT_K)L_J^{JK}, \qquad (2.1)$$

see Section 2.4. Hence, the DFT of f at  $\omega$  is essentially performed by:

- 1.  $K^{e-1}$  DFT's of size K (that is, DFT's on polynomials of degree at most K-1),

- 2. N multiplications by a power of  $\omega$  (coming from the diagonal matrix  $D_{J,K}$ ) and

- 3. K DFT's of size  $K^{e-1}$ .

Unrolling Formula (2.1) so as to replace  $DFT_J$  by  $DFT_K$  and the other linear operators involved (the diagonal matrix D and the permutation matrix L) one can see that a DFT of size  $N = K^e$  reduces to:

- 1.  $e K^{e-1}$  DFT's of size K, and

- 2. (e-1)N multiplication by a power of  $\omega$ .

Recall that the assumption on the cost of a multiplication by  $\eta^i$ , for  $0 \le i < K$ , makes the cost for one DFT of size K to  $O(K \log_2(K)k)$  machine-word operations. Hence, all the DFT's of size K together amount to  $O(e \ N \log_2(K)k)$  machine-word operations. That is,  $O(N \log_2(N)k)$  machine-word operations. Meanwhile, the total cost of the multiplication by a power of  $\omega$  is  $O(e \ N \ M(k))$  machine-word operations, that is,  $O(N \log_K(N) \ M(k))$  machine-word operations. Indeed, multiplying an arbitrary element of  $\mathbb{Z}/p\mathbb{Z}$  by an arbitrary power of  $\omega$  requires O(M(k)) machine-word operations. Therefore, under our assumption, a

DFT of size N at  $\omega$  amounts to

$$O(N \log_2(N) k + N \log_K(N) M(k))$$

(2.2)

machine-word operations. When using generalized Fermat primes, we have K = 2k and the above estimate becomes

$$O(N \log_2(N) k + N \log_k(N) M(k))$$

(2.3)

The second term in the big-O notation dominates the first one. However, we keep both terms for reasons that will appear shortly.

Without our assumption, as discussed earlier, the same DFT would run in  $O(N \log_2(N) M(k))$  machine-word operations. Therefore, using generalized Fermat primes brings a speedup factor of  $\log(K)$  w.r.t. the direct approach using arbitrary prime numbers.

At this point, it is natural to ask what would be the cost of a comparable computation using small primes and the CRT. To be precise, let us consider the following problem. Let  $p_1, \ldots, p_k$  be pairwise different prime numbers of machine-word size and let m be their product. Assume that N divides each of  $p_1-1,\ldots,p_k-1$  such that each of fields  $\mathbb{Z}/p_1\mathbb{Z},\ldots,\mathbb{Z}/p_k\mathbb{Z}$  admits an N-th primitive roots of unity,  $\omega_1,\ldots,\omega_k$ . Then,  $\omega=(\omega_1,\ldots,\omega_k)$  is an N-th primitive root of  $\mathbb{Z}/m\mathbb{Z}$ . Indeed, the ring  $\mathbb{Z}/p_1\mathbb{Z}\otimes\cdots\otimes\mathbb{Z}/p_k\mathbb{Z}$  is a direct product of fields. Let  $f\in\mathbb{Z}/m\mathbb{Z}[x]$  be a polynomial of degree N-1. One can compute the DFT of f at  $\omega$  in three steps:

- 1. Compute the images  $f_1 \in \mathbb{Z}/p_1\mathbb{Z}[x], \ldots, f_k \in \mathbb{Z}/p_k\mathbb{Z}[x]$  of f.

- 2. Compute the DFT of  $f_i$  at  $\omega_i$  in  $\mathbb{Z}/p_i\mathbb{Z}[x]$ , for i = 1, ..., k,

- 3. Combine the results using CRT so as to obtain a DFT of f at  $\omega$ .

The first and the third above steps will run within  $O(N \times M(k) \log_2(k))$  machine-word operations meanwhile the second one amount to  $O(k \times N \log(N))$  machine-word operations, yielding a total of

$$O(N \log_2(N) k + N M(k) \log_2(k))$$

$$(2.4)$$

These estimates yield a running-time ratio between the two approaches of  $\log(N)/\log_2^2(k)$ , which suggests that for k large enough the big prime field approach may outperform the CRT-based approach. We believe that this analysis is part of the explanation for the observation that the two approaches are, in fact, competitive in practice, as we shall see in Section 3.5.

We conclude this section by observing that, in the above, we have focused our discussion on algebraic complexity, thus not considering the question of cache complexity. We note that for small prime fields, FFTs that are optimal in terms of cache complexity can be derived easily from the results of [22]. For big prime fields, the same results could be adapted to derive cache complexity optimal FFTs. We leave that for future work. Nevertheless, we can already observe that when the big prime is large enough for one multiplication in the big prime field to fully occupy the L1 cache, then the naive 2-way divide-and-conquer FFT becomes essentially cache complexity optimal.

#### 2.3 Generalized Fermat numbers

The *n*-th Fermat number, denoted by  $F_n$ , is given by  $F_n = 2^{2^n} + 1$ . This sequence plays an important role in number theory and, as mentioned in the introduction, in the development of asymptotically fast algorithms for integer multiplication [23, 21].

Arithmetic operations modulo a Fermat number are simpler than modulo an arbitrary positive integer. In particular 2 is a  $2^{n+1}$ -th primitive root of unity modulo  $F_n$ . Unfortunately,  $F_4$  is the largest Fermat number which is known to be prime. Hence, when computations require the coefficient ring be a field, Fermat numbers are no longer interesting. This motivates the introduction of other family of Fermat-like numbers, see, for instance, Chapter 2 in the text book *Guide to elliptic curve cryptography* [24].

Numbers of the form  $a^{2^n} + b^{2^n}$  where a > 1,  $b \ge 0$  and  $n \ge 0$  are called *generalized Fermat numbers*. An odd prime p is a generalized Fermat number if and only if p is congruent to 1 modulo 4. The case b = 1 is of particular interest and, by analogy with the ordinary Fermat numbers, it is common to denote the generalized Fermat number  $a^{2^n} + 1$  by  $F_n(a)$ . So 3 is  $F_0(2)$ . We call a the radix of  $F_n(a)$ . Note that, Landau's fourth problem asks if there are infinitely many generalized Fermat primes  $F_n(a)$  with n > 0.

In the finite ring  $\mathbb{Z}/F_n(a)\mathbb{Z}$ , the element a is a  $2^{n+1}$ -th primitive root of unity. However, when using binary representation for integers on a computer, arithmetic operations in  $\mathbb{Z}/F_n(a)\mathbb{Z}$  may not be as easy to perform as in  $\mathbb{Z}/F_n\mathbb{Z}$ . This motivates the following.

**Definition 1** We call sparse radix generalized Fermat number, any integer of the form  $F_n(r)$  where r is either  $2^w + 2^u$  or  $2^w - 2^u$ , for some integers  $w > u \ge 0$ . In the former case, we denote  $F_n(r)$  by  $F_n^+(w, u) = 2^w + 2^u$  and in the latter by  $F_n^-(w, u) = 2^w - 2^u$ .

Table 2.1 lists sparse radix generalized Fermat numbers (SRGFNs) that are prime. For each such number p, we give the largest power of 2 dividing p-1, that is, the maximum length N of a vector to which a radix-K FFT algorithm where K is an appropriate power of 2.

**Notation 1** In the sequel, we consider  $p = F_n(r)$ , a fixed SRGFN. We denote by  $2^e$  the largest power of 2 dividing p - 1 and we define  $k = 2^n$ , so that  $p = r^k + 1$  holds.

As we shall see in the sequel of this section, for any positive integer N which is a power of 2 such that N divides p-1, one can find an N-th primitive root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that multiplying an element  $x \in \mathbb{Z}/p\mathbb{Z}$  by  $\omega^{i(N/2k)}$  for  $0 \le i < 2k$  can be done in linear time w.r.t. the bit size of x. Combining this observation with an appropriate factorization of the DFT transform on N points over  $\mathbb{Z}/p\mathbb{Z}$ , we obtain an efficient FFT algorithm over  $\mathbb{Z}/p\mathbb{Z}$ .

| p                             | $\max\{2^e \text{ s.t. } 2^e \mid p-1\}$ |

|-------------------------------|------------------------------------------|

| $(2^{63} + 2^{53})^2 + 1$     | $2^{106}$                                |

| $(2^{64} - 2^{50})^4 + 1$     | 2 <sup>200</sup>                         |

| $(2^{63} + 2^{34})^8 + 1$     | 2 <sup>272</sup>                         |

| $(2^{62} + 2^{36})^{16} + 1$  | 2 <sup>576</sup>                         |

| $(2^{62} + 2^{56})^{32} + 1$  | 2 <sup>1792</sup>                        |

| $(2^{63} - 2^{40})^{64} + 1$  | 2 <sup>2560</sup>                        |

| $(2^{64} - 2^{28})^{128} + 1$ | 2 <sup>3584</sup>                        |

Table 2.1: SRGFNs of practical interest.

## 2.3.1 Representation of $\mathbb{Z}/p\mathbb{Z}$

We represent each element  $x \in \mathbb{Z}/p\mathbb{Z}$  as a vector  $\vec{x} = (x_{k-1}, x_{k-2}, \dots, x_0)$  of length k and with non-negative integer coefficients such that we have

$$x \equiv x_{k-1} r^{k-1} + x_{k-2} r^{k-2} + \dots + x_0 \mod p. \tag{2.5}$$

This representation is made unique by imposing the following constraints

- 1. either  $x_{k-1} = r$  and  $x_{k-2} = \cdots = x_1 = 0$ ,

- 2. or  $0 \le x_i < r$  for all i = 0, ..., (k-1).

We also map x to a univariate integer polynomial  $f_x \in \mathbb{Z}[T]$  defined by  $f_x = \sum_{i=0}^{k-1} x_i t^i$  such that  $x \equiv f_x(r) \mod p$ .

Now, given a non-negative integer x < p, we explain how the representation  $\vec{x}$  can be computed. The case  $x = r^k$  is trivially handled, hence we assume  $x < r^k$ . For a non-negative integer z such that  $z < r^{2^i}$  holds for some positive integer  $i \le n = \log_2(k)$ , we denote by vec(z, i) the unique sequence of  $z^i$  non-negative integers  $(z_{2^{i-1}}, \ldots, z_0)$  such that we have  $0 \le z_i < r$  and  $z = z_{2^{i-1}} r^{2^{i-1}} + \cdots + z_0$ . The sequence vec(z, i) is obtained as follows:

- 1. if i = 1, we have vec(z, i) = (q, s),

- 2. if i > 1, then vec(z, i) is the concatenation of vec(q, i 1) followed by vec(s, i 1),

where q and s are the quotient and the remainder in the Euclidean division of z by  $r^{2^{i-1}}$ . Clearly,  $\text{vec}(x, n) = \vec{x}$  holds.

We observe that the sparse binary representation of r facilitates the Euclidean division of a non-negative integer z by r, when performed on a computer. Referring to the notations in Definition 1, let us assume that r is  $2^w + 2^u$ , for some integers  $w > u \ge 0$ . (The case  $2^w - 2^u$  would be handled in a similar way.) Let  $z_{\text{high}}$  and  $z_{\text{low}}$  be the quotient and the remainder in

the Euclidean division of z by  $2^w$ . Then, we have

$$z = 2^{w} z_{\text{high}} + z_{\text{low}} = r z_{\text{high}} + z_{\text{low}} - 2^{u} z_{\text{high}}.$$

(2.6)

Let  $s = z_{\text{low}} - 2^{u}z_{\text{high}}$  and  $q = z_{\text{high}}$ . Three cases arise:

- (S1) if  $0 \le s < r$ , then q and s are the quotient and remainder of z by r,

- (S2) if  $r \leq s$ , then we perform the Euclidean division of s by r and deduce the desired quotient and remainder,

- (S3) if s < 0, then (q, s) is replaced by (q + 1, s + r) and we go back to Step (S1).

Since the binary representations of  $r^2$  can still be regarded as sparse, a similar procedure can be done for the Euclidean division of a non-negative integer z by  $r^2$ . For higher powers of r, we believe that Montgomery multiplication [25] is the way to go, though this remains to be explored.

## 2.3.2 Finding primitive roots of unity in $\mathbb{Z}/p\mathbb{Z}$

**Notation 2** Let N be a power of 2, say  $2^{\ell}$ , dividing p-1 and let  $g \in \mathbb{Z}/p\mathbb{Z}$  be an N-th primitive root of unity.

Recall that such an N-th primitive root of unity can be obtained by a simple probabilistic procedure. Write p=qN+1. Pick a random  $\alpha\in\mathbb{Z}/p\mathbb{Z}$  and let  $\omega=\alpha^q$ . Little Fermat theorem implies that either  $\omega^{N/2}=1$  or  $\omega^{N/2}=-1$  holds. In the latter case,  $\omega$  is an N-th primitive root of unity. In the former, another random  $\alpha\in\mathbb{Z}/p\mathbb{Z}$  should be considered. In our various software implementation of finite field arithmetic [26, 27, 28], this procedure finds an N-th primitive root of unity after a few tries and has never been a performance bottleneck.

In the following, we consider the problem of finding an N-th primitive root of unity  $\omega$  such that  $\omega^{N/2k} = r$  holds. The intention is to speed up the portion of FFT computation that requires to multiply elements of  $\mathbb{Z}/p\mathbb{Z}$  by powers of  $\omega$ .

**Proposition 1** In  $\mathbb{Z}/p\mathbb{Z}$ , the element r is a 2k-th primitive root of unity. Moreover, the following algorithm computes an N-th primitive root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that we have  $\omega^{N/2k} = r$  in  $\mathbb{Z}/p\mathbb{Z}$ .

**Proof** Since  $g^{N/2k}$  is a 2k-th root of unity, it is equal to  $r^{i_0}$  (modulo p) for some  $0 \le i_0 < 2k$  where  $i_0$  is odd. Let j be a non-negative integer. Observe that we have

$$g^{j2^{\ell}/2k} = (g^i g^{2kq})^{2^{\ell}/2k} = g^{i2^{\ell}/2k} = r^{i i_0},$$

(2.7)

where q and i are quotient and the remainder of j in the Euclidean division by 2k. By definition of g, the powers  $g^{i2^{\ell}/2k}$ , for  $0 \le i < 2k$ , are pairwise different. It follows from Formula (2.7) that the elements  $r^{i}$  are pairwise different as well, for  $0 \le i < 2k$ . Therefore, one of

**Algorithm 1** Find a primitive *N*-th root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that  $\omega^{N/2k} = r$ .

#### input:

- Exponent *N*.

- Radix r and exponent k from  $p = r^k + 1$ .

- An *N*-th root of unity  $g \in \mathbb{Z}/p\mathbb{Z}$ .

#### output:

- An *N*-th primitive root of unity  $\omega \in \mathbb{Z}/p\mathbb{Z}$  such that  $\omega^{N/2k} = r$ .

```

procedure PrimitiveRootAsRootOf(N, r, k, g)

\alpha := g^{N/2k}

\beta := \alpha

j := 1

while \beta \neq r do

\beta := \alpha\beta

j := j + 1

end while

\omega := g^j

return (\omega)

end procedure

```

those latter elements is r itself. Hence, we have  $j_1$  with  $0 \le j_1 < 2k$  such that  $g^{j_1N/2k} = r$ . Then,  $\omega = g^{j_1}$  is as desired and Algorithm 1 computes it.  $\square$

## 2.3.3 Addition and subtraction in $\mathbb{Z}/p\mathbb{Z}$

Let  $x, y \in \mathbb{Z}/p\mathbb{Z}$  represented by  $\vec{x}, \vec{y}$ , see Section 2.3.1 for this latter notation. Algorithm 2 computes the representation  $\vec{x} + \vec{y}$  of the element  $(x + y) \mod p$ .

**Proof** At Step (1),  $\vec{x}$  and  $\vec{y}$ , regarded as vectors over  $\mathbb{Z}$ , are added component-wise. At Steps (2) and (3), the carry, if any, is propagated. At Step (4), there is no carry beyond the leading digit  $z_{k-1}$ , hence  $(z_{k-1}, \ldots, z_0)$  represents x + y. Step (5) handles the special case where x + y = p - 1 holds. Step (6) is the *overflow* case which is handled by subtracting 1 mod p to  $(z_{k-1}, \ldots, z_0)$ , finally producing  $\overrightarrow{x + y}$ .  $\square$

A similar procedure computes the vector  $\overrightarrow{x-y}$  representing the element  $(x-y) \in \mathbb{Z}/p\mathbb{Z}$ . Recall that we explained in Section 2.3.1 how to perform the Euclidean divisions at Step (S3) in a way that exploits the sparsity of the binary representation of r.

In practice, the binary representation of the radix r fits a machine word, see Table 2.1. Consequently, so does each of the "digit" in the representation  $\vec{x}$  of every element  $x \in \mathbb{Z}/p\mathbb{Z}$ . This allows us to exploit machine arithmetic in a sharper way. In particular, the Euclidean divisions at Step (S3) can be further optimized.

### **Algorithm 2** Computing $x + y \in \mathbb{Z}/p\mathbb{Z}$ for $x, y \in \mathbb{Z}/p\mathbb{Z}$

#### input:

- Elements  $x, y \in \mathbb{Z}/p\mathbb{Z}$  represented by  $\vec{x}, \vec{y}$ .

- Radix r and exponent k from  $p = r^k + 1$ .

#### output:

- Result of addition x + y.

#### **procedure** BigPrimeFieldAddition( $\vec{x}$ , $\vec{y}$ , r, k)

- 1: compute  $z_i = x_i + y_i$  in  $\mathbb{Z}$ , for  $i = 0, \dots, k-1$ ,

- 2: let  $z_k = 0$ ,

- 3: for i = 0, ..., k 1, compute the quotient  $q_i$  and the remainder  $s_i$  in the Euclidean division of  $z_i$  by r, then replace  $(z_{i+1}, z_i)$  by  $(z_{i+1} + q_i, s_i)$ ,

- 4: if  $z_k = 0$  then return  $(z_{k-1}, ..., z_0)$ ,

- 5: if  $z_k = 1$  and  $z_{k-1} = \cdots = z_0 = 0$ , then let  $z_{k-1} = r$  and return  $(z_{k-1}, \ldots, z_0)$ ,

- 6: let  $i_0$  be the smallest index,  $0 \le i_0 \le k$ , such that  $z_{i_0} \ne 0$ , then let  $z_{i_0} = z_{i_0} 1$ , let  $z_0 = \cdots = z_{i_0-1} = r 1$  and return  $(z_{k-1}, \ldots, z_0)$ .

#### end procedure

#### 2.3.4 Multiplication by a power of r in $\mathbb{Z}/p\mathbb{Z}$

Before considering the multiplication of two arbitrary elements  $x, y \in \mathbb{Z}/p\mathbb{Z}$ , we assume that one of them, say y, is a power of r, say  $y = r^i$  for some 0 < i < 2k. Note that the cases i = 0 = 2k are trivial. Indeed, recall that r is a 2k-th primitive root of unity in  $\mathbb{Z}/p\mathbb{Z}$ . In particular,  $r^k = -1$  in  $\mathbb{Z}/p\mathbb{Z}$ . Hence, for 0 < i < k, we have  $r^{k+i} = -r^i$  in  $\mathbb{Z}/p\mathbb{Z}$ . Thus, let us consider first the case where 0 < i < k holds. We also assume  $0 \le x < r^k$  holds in  $\mathbb{Z}$ , since the case  $x = r^k$  is easy to handle. From Equation (2.5) we have:

$$xr^{i} \equiv (x_{k-1}r^{k-1+i} + \dots + x_{0}r^{i}) \mod p$$

$$\equiv \sum_{j=0}^{j=k-1} x_{j}r^{j+i} \mod p$$

$$\equiv \sum_{h=i}^{h=k-1+i} x_{h-i}r^{h} \mod p$$

$$\equiv (\sum_{h=i}^{h=k-1} x_{h-i}r^{h} - \sum_{h=k}^{h=k-1+i} x_{h-i}r^{h-k}) \mod p$$

The case k < i < 2k can be handled similarly. Also, in the case i = k we have  $xr^i = x(p-1) = -x$  in  $\mathbb{Z}/p\mathbb{Z}$ . It follows, that for all 0 < i < 2k, computing the product x  $r^i$  simply reduces to computing a subtraction. This fact, combined with Proposition 1, motivates the development of FFT algorithms over  $\mathbb{Z}/p\mathbb{Z}$ .

2.4 FFT Basics

#### 2.3.5 Multiplication in $\mathbb{Z}/p\mathbb{Z}$

Let again  $x, y \in \mathbb{Z}/p\mathbb{Z}$  represented by  $\vec{x}, \vec{y}$  and consider the univariate polynomials  $f_x, f_y \in \mathbb{Z}[T]$  associated with x, y; see Section 2.3.1 for this notation. To compute the product x y in  $\mathbb{Z}/p\mathbb{Z}$ , we proceed as follows.

#### **Algorithm 3** Computing $xy \in \mathbb{Z}/p\mathbb{Z}$ for $x, y \in \mathbb{Z}/p\mathbb{Z}$

#### input:

- Polynomials  $f_x$ ,  $f_y \in \mathbb{Z}[T]$  associated with  $x, y \in \mathbb{Z}/p\mathbb{Z}$ .

- Radix r and exponent k from  $p = r^k + 1$ .

#### output:

- Result of multiplication *xy*.

**procedure** BigPrimeFieldMultiplication( $f_x$ ,  $f_y$ , r, k)

- 1: We compute the polynomial product  $f_u = f_x f_y$  in  $\mathbb{Z}[T]$  modulo  $T^k + 1$ .

- 2: Writing  $f_u = \sum_{i=0}^{k-1} u_i T^i$ , we observe that for all  $0 \le i \le k-1$  we have  $0 \le u_i \le kr^2$  and compute a representation  $\overrightarrow{u_i}$  of  $u_i$  in  $\mathbb{Z}/p\mathbb{Z}$  using the method explained in Section 2.3.1.

- 3: We compute  $u_i r^i$  in  $\mathbb{Z}/p\mathbb{Z}$  using the method of Section 2.3.4.

- 4: Finally, we compute the sum  $\sum_{i=0}^{k-1} u_i r^i$  in  $\mathbb{Z}/p\mathbb{Z}$  using Algorithm 2.

#### end procedure

For large values of k,  $f_x f_y \mod T^k + 1$  in  $\mathbb{Z}[T]$  can be computed by asymptotically fast algorithms (see the paper [29, 18]). However, for small values of k (say  $k \le 8$ ), using plain multiplication is reasonable.

#### 2.4 FFT Basics

We review the Discrete Fourier Transform over a finite field, and its related concepts. See [21] for details.

**Primitive and principal roots of unity.** Let  $\mathcal{R}$  be a commutative ring with units. Let N>1 be an integer. An element  $\omega\in\mathcal{R}$  is a *primitive* N-th root of unity if for  $1< k\leq N$  we have  $\omega^k=1\iff k=N$ . The element  $\omega\in\mathcal{R}$  is a *principal* N-th root of unity if  $\omega^N=1$  and for all  $1\leq k< N$  we have

$$\sum_{j=0}^{N-1} \omega^{jk} = 0. {(2.8)}$$

In particular, if N is a power of 2 and  $\omega^{N/2}=-1$ , then  $\omega$  is a principal N-th root of unity. The two notions coincide in fields of characteristic 0. For integral domains every primitive root of unity is also a principal root of unity. For non-integral domains, a principal N-th root of unity is also a primitive N-th root of unity unless the characteristic of the ring  $\mathcal R$  is a divisor of N.

The discrete Fourier transform (DFT). Let  $\omega \in \mathcal{R}$  be a principal N-th root of unity. The N-point DFT at  $\omega$  is the linear function, mapping the vector  $\vec{a} = (a_0, \ldots, a_{N-1})^T$  to  $\vec{b} = (b_0, \ldots, b_{N-1})^T$  by  $\vec{b} = \Omega \vec{a}$ , where  $\Omega = (\omega^{jk})_{0 \le j,k \le N-1}$ . If N is invertible in  $\mathcal{R}$ , then the N-point DFT at  $\omega$  has an inverse which is 1/N times the N-point DFT at  $\omega^{-1}$ .

The fast Fourier transform. Let  $\omega \in \mathcal{R}$  be a principal N-th root of unity. Assume that N can be factorized to JK with J, K > 1. Recall Cooley-Tukey factorization formula [30]

$$DFT_{JK} = (DFT_J \otimes I_K)D_{J,K}(I_J \otimes DFT_K)L_J^{JK}, \qquad (2.9)$$

where, for two matrices A, B over  $\mathcal{R}$  with respective dimensions  $m \times n$  and  $q \times s$ , we denote by  $A \otimes B$  an  $mq \times ns$  matrix over  $\mathcal{R}$  called the tensor product of A by B and defined by

$$A \otimes B = [a_{k\ell}B]_{k,\ell} \quad \text{with} \quad A = [a_{k\ell}]_{k,\ell}. \tag{2.10}$$

In the above formula,  $\mathrm{DFT}_{JK}$ ,  $\mathrm{DFT}_J$  and  $\mathrm{DFT}_K$  are respectively the N-point DFT at  $\omega$ , the J-point DFT at  $\omega^K$  and the K-point DFT at  $\omega^J$ . The *stride permutation matrix*  $L_J^{JK}$  permutes an input vector  $\mathbf{x}$  of length JK as follows

$$\mathbf{x}[iJ+j] \mapsto \mathbf{x}[jK+i],\tag{2.11}$$

for all  $0 \le j < J$ ,  $0 \le i < K$ . If **x** is viewed as a  $K \times J$  matrix, then  $L_J^{JK}$  performs a transposition of this matrix. The *diagonal twiddle matrix*  $D_{I,K}$  is defined as

$$D_{J,K} = \bigoplus_{j=0}^{J-1} \operatorname{diag}(1, \omega^j, \dots, \omega^{j(K-1)}),$$

(2.12)

Formula (2.9) implies various divide-and-conquer algorithms for computing DFTs efficiently, often referred to as fast Fourier transforms (FFTs). See the papers [5] and [7] by the authors of the SPIRAL and FFTW projects, respectively. This formula also implies that, if K divides J, then all involved multiplications are by powers of  $\omega^K$ .

#### 2.5 Blocked FFT on the GPU

In the sequel of this section, let  $\omega \in \mathcal{R}$  be a principal N-th root of unity. In the factorization of the matrix DFT $_{IK}$ , viewing the size K as a base case and assuming that J is a power of K,

Formula (2.9) translates into a recursive algorithm. This recursive formulation is, however, not appropriate for generating code targeting many-core GPU-like architectures for which, formulating algorithms iteratively facilitates the division of the work into kernel calls and thread-blocks. To this end, we shall unroll Formula (2.9).

**Notation 3** Assuming c = 0, that is,  $N = K^e$ , we define the following linear operators, for i = 0, ..., e - 1:

$$U_{i}(\omega) = \begin{pmatrix} I_{K^{i}} \otimes \mathrm{DFT}_{K}(\omega^{K^{e-1}}) \otimes I_{K^{e-i-1}} \end{pmatrix} \cdot \begin{pmatrix} I_{K^{i}} \otimes D_{K,K^{e-i-1}}(\omega^{K^{i}}) \end{pmatrix},$$

$$V_{i}(\omega) = I_{K^{i}} \otimes L_{K}^{K^{e-i}},$$

$$W_{i}(\omega) = I_{K^{i}} \otimes \left( L_{K^{e-i-1}}^{K^{e-i}} \cdot D_{K,K^{e-i-1}}(\omega^{K^{i}}) \right).$$

$$(2.13)$$

**Remark 1** We recall two classical formulas for tensor products of matrices. If A and B are square matrices over R with respective orders a and b, then we have

$$A \otimes B = L_a^{ab} \cdot (B \otimes A) L_b^{ab}. \tag{2.14}$$

If C and D are two other square matrices over R with respective orders a and b, then we have

$$(A \otimes B) \cdot (C \otimes D) = (A \cdot C) \otimes (B \cdot D). \tag{2.15}$$

Our GPU implementation reported in Section 2.6 is based on the following two results. We omit the proofs, which can easily be derived from Remark 1 and the Cooley-Tukey factorization formula; see [14]. Computer program code can be generated from Proposition 3 using the techniques of [5].

**Proposition 2** For i = 0, ..., e - 1, we have

$$U_i(\omega) = V_i(\omega) \left( I_{K^{e-1}} \otimes DFT_K(\omega^{K^{e-1}}) \right) W_i(\omega)$$

(2.16)

The following formula reduces the computation of a DFT on  $K^e$  points to computing e DFT's on K points.

**Proposition 3** The following factorization of DFT<sub> $K^e$ </sub>( $\omega$ ) holds:

$$DFT_{K^{e}}(\omega) = U_{0}(\omega) \cdots U_{e-1}(\omega) V_{e-1}(\omega) \cdots V_{0}(\omega). \tag{2.17}$$

## 2.6 Implementation

In this section, we discuss implementation techniques. Our experimental results are reported in Section 3.5. We have realized a GPU implementation in the CUDA language of the algorithms presented in Sections 2.3 and 2.5. We have used the third and the fourth Generalized Fermat primes from Table 1, namely  $P_3 := (2^{63} + 2^{34})^8 + 1$  and  $P_4 := (2^{62} + 2^{36})^{16} + 1$ . We have tested our code and collected the experimental data on three different types of GPU cards.

**Parallelization.** Performing arithmetic operations on vectors of elements of  $\mathbb{Z}/p\mathbb{Z}$  has inherent data parallelism, which is ideal for implementation on GPUs. In our implementation, each arithmetic operation is computed by one thread. An alternative approach would be to use multiple threads for computing one operation. However, this would not improve performance mostly due to overhead of handling carry propagation (in the case of addition and subtraction), or increased latency because of frequent accesses to global memory (in the case of twiddle factor multiplications).

Memory-bound kernels. Performance of our GPU kernels are limited by frequent accesses to memory. Therefore, we have considered solutions for minimizing memory latency, maximizing occupancy (i.e. number of active warps on each streaming multiprocessor) to hide latency, and maximizing IPC (instructions per clock cycle).

**Location of data.** At execution time, each thread needs to perform computation on at least one element of  $\mathbb{Z}/p\mathbb{Z}$ , meaning that it will read/write at least k digits of machine-word size. Often, in such a scenario, shared memory is utilized as an auxiliary memory, but this approach has two shortcomings. First, on a GPU, each streaming multiprocessor has a limited amount of shared memory which might not be large enough for allowing each thread to keep at least one element of  $\mathbb{Z}/p\mathbb{Z}$  (since the value of k can be quite large). Second, using a huge amount of shared memory will reduce occupancy. At the same time, there is no opportunity for using texture memory or constant memory when computing over  $\mathbb{Z}/p\mathbb{Z}$ . Conclusively, the only remaining solution is to keep all data on global memory.

Maximizing global memory efficiency. Assume that for a vector of N elements of  $\mathbb{Z}/p\mathbb{Z}$ , consecutive digits of each element of  $\mathbb{Z}/p\mathbb{Z}$  are stored in adjacent memory addresses. Therefore, such a vector can be considered as the row-major layout of a matrix with N rows and k columns. In practice, this data structure will hurt performance due to increased memory overhead, caused by non-coalesced accesses to global memory. In this case, an effective solution is to apply a stride permutation  $L_k^{kN}$  on all input vectors (if data is stored in a row-major layout, this permutation is equivalent to transposing the input to a matrix of k rows and N columns). Therefore, all kernels are written with the assumption that consecutive digits of the same element are N steps away from each other in the memory. As a result, accesses to global memory will be coalesced, increasing memory load and store efficiency, and lowering the memory overhead.

Decomposing computation into multiple kernels. Inside a kernel, consuming too many reg-

2.7 Experimentation 17

isters per thread can lower occupancy, or even worse, lead to register spilling. In order to prevent from register spilling, register-intensive kernels are broken into multiple smaller kernels.

**Size of thread blocks.** Our GPU kernels do not depend on the size of a thread block. So, we choose a configuration for a thread block that will maximize the percentage of occupancy, the value of IPC (instruction per clock cycle), and bandwidth-related performance metrics such as the load and store throughput. We have achieved the best experimental results for thread blocks of 128 threads, or 256 threads.

Effect of GPU instructions on performance. Our current implementation is optimized for the primes  $P_3 := (2^{63} + 2^{34})^8 + 1$  and  $P_4 := (2^{62} + 2^{36})^{16} + 1$ . Therefore, we rely on 64-bit instructions on GPUs. As it is explained in [31], even though 64-bit integer instructions are supported on NVIDIA GPUs, at compile time, all arithmetic and memory instructions will first be converted to a sequence of 32-bit equivalents. This might have a negative impact on the overall performance of our implementation. Specially, compared to addition and subtraction, 64-bit multiplication is computed through a longer sequence of 32-bit instructions. Finally, using 32-bit arithmetic provides more opportunities for optimization such as instruction level parallelism.

## 2.7 Experimentation

We compare our implementation of FFT over a big prime field against a comparable approach based on FFTs over small prime fields. To be precise, we implement the two approaches discussed in Section 2.2. Recall that the first approach computes an FFT of size N over a big prime field of the form  $\mathbb{Z}/p\mathbb{Z}$  where p is a SRGFN of size k machine words. The second approach uses s=2 k half-machine word primes  $p_1,\ldots,p_s$  and proceeds as follows:

- 1. **projection:** compute the image  $f_i$  of f in  $\mathbb{Z}/p_1\mathbb{Z}[x], \ldots, \mathbb{Z}/p_k\mathbb{Z}[x]$ , for  $i = 1, \ldots, k$ ,

- 2. *images*: compute the DFT of  $f_i$  at  $\omega_i$  in  $\mathbb{Z}/p_i\mathbb{Z}[x]$ , for  $i=1,\ldots,k$  (using the CUMODP library [14]),

- 3. *combination:* combine the results using CRT so as to obtain a DFT of f at  $\omega$ .

We use half-machine word primes (instead of machine-word primes as discussed in Section 2.2) because the small prime field FFTs of the CUMODP library impose this choice. Experimental results are gathered in Section 2.7.1.

We also have implemented and tested a sequential, CPU version of both approaches. For the small prime field approach, we use the NTL library [11], supporting FFT modulo machineword size primes of 60 bits. However, for the big prime field approach, we have implemented our own arithmetic in a sequential C program. Experimental results are gathered in Section 2.7.2.

#### 2.7.1 Big prime vs. small prime on the GPU

The output of the two approaches is the DFT of a vector of size N over a ring R which is either a prime field or a direct product of prime fields, and for which each element spans k machinewords. Hence these two approaches are equivalent building blocks in a modular method. For realizing the benchmark, first, we perform the reduction step, followed by computing s = 2k FFTs of size N over small prime fields. In the small field case, we use the highly optimized implementation of the following FFT algorithms from the CUMODP library (see [14, 15] and [28]): the Cooley-Tukey FFT algorithm (CT), the Cooley-Tukey FFT algorithm with precomputed powers of the primitive root (CT-pow), and the Stockham FFT algorithm. The above codes compute DFTs for input vectors of  $2^n$  elements, where  $20 \le n \le 26$  is typical.

Our CUDA implementation of the big prime field approach computes DFT over  $\mathbb{Z}/p\mathbb{Z}$ , for  $P_3 := (2^{63} + 2^{34})^8 + 1$  and  $P_4 := (2^{62} + 2^{36})^{16} + 1$ , and input vectors of size  $N = K^e$  where K = 16 for  $P_3$ , and K = 32 for  $P_4$ . Furthermore, for  $P_3$ , we have  $2 \le e \le 5$ , while for  $P_4$  (due to the limited size of global memory on a GPU card), we have  $2 \le e \le 4$ .

The benchmark is computed on an NVIDIA Geforce GTX 760M (CC 3.0), an NVIDIA Tesla C2075 (CC 2.0), and an NVIDIA Tesla M2050 (CC 2.0). The first card has effective bandwidth of 48 GB/s, with 4 streaming multiprocessor, and the total number of 768 CUDA cores.

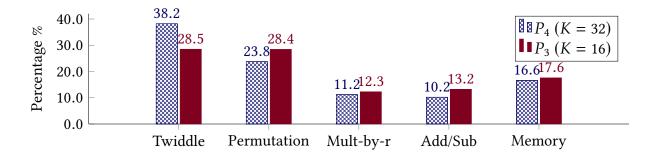

Figures 2.1 and 2.2 show the speedup of the big prime field FFT compared to the small prime field approach, measured on the first GPU card. Moreover, Table 2.2 presents the running times of computing the benchmark on the mentioned GPU cards. In each table, the first three columns give the running times for computing the small prime field FFT based on the Cooley-Tukey algorithm, the Cooley-Tukey FFT algorithm with precomputed powers of the primitive root, and the Stockham algorithm, respectively. Meanwhile, the last column presents the running time for computing the big prime field FFT.

As it is reported in [14], the FFT algorithms of the CUMODP library gain speedup factors for vectors of the size  $2^{16}$  and larger, therefore, the input vector should be large enough to keep the GPU device busy, and thus, provide a high percentage of occupancy. This explains the results displayed on Figures 2.1 and 2.2; for both primes  $P_3$  and  $P_4$ , when  $N = K^2$  and  $N = K^3$ , our big prime field FFT approach significantly outperforms the small prime field FFT approach.

More importantly, for both primes  $P_3$  and  $P_4$ , and with vectors of size  $N = K^4$ , our experimental results demonstrate that computing the big prime field FFT is competitive with the small prime field approach in terms of running time. For both primes  $P_3$  and  $P_4$ , we can compute FFT for an input vector of size  $N = K^4$ , which is equivalent of  $2^{16}$  and  $2^{20}$  elements, respectively, and is large enough to cover many practical applications.

Eventually, for  $P_3$ , and for a vector of size  $N = K^5$ , the Cooley-Tukey (with precomputation) and Stockham FFT codes are slightly faster than the big prime field FFT. Nevertheless, for each of the tested big primes, there is a bit size range of input vectors over which the big prime

2.7 Experimentation 19

field approach outperforms the small prime approach, which is coherent with the analysis of Section 2.2. For  $P_3 := (2^{63} + 2^{34})^8 + 1$ , this range is  $[2^{12}, 2^{16}]$  while for  $P_4 := (2^{62} + 2^{36})^{16} + 1$ , this range is  $[2^{15}, 2^{20}]$ . Our GPU implementation of the big prime field arithmetic is generic and thus can support larger SRGFNs, see Table 1.

Table 2.2: Running time of computing the benchmark for  $N = K^e$  on GPU (timings in milliseconds).

| ( | Computing the benchmark for $N = K^e$ for $P_3 := (2^{63} + 2^{34})^8 + 1 (K = 16)$ |           |             |         | Computing the benchmark for $N = K^e$<br>for $P_4 := (2^{62} + 2^{36})^{16} + 1 (K = 32)$ |   |          |            |             |         |

|---|-------------------------------------------------------------------------------------|-----------|-------------|---------|-------------------------------------------------------------------------------------------|---|----------|------------|-------------|---------|

| Ν | /leasured                                                                           | on a NVII | OIA GTX-760 | M GPU   | Measured on NVIDIA GTX-760M GPU                                                           |   |          |            | M GPU       |         |

| e | CT                                                                                  | CT-pow    | Stockham    | Big FFT | -                                                                                         | e | CT       | CT-pow     | Stockham    | Big FFT |